A COMPANY OF THE SWATCH GROUP

# 40 Segment Static LCD Driver

## Features

- Serial data input / output

- Low dynamic current, 5 µA max.

- Low standby current, 1  $\mu$ A max.

- Separate input and display voltages

- Wide power supply range:

- $V_{\text{DD}}$  (logic) 2 to 8 V,  $V_{\text{LCD}}$  (display)  $V_{\text{DD}}$  to 12 V

- On-chip latches separate control and display sections

- Drives up to 40 LCD segments in direct drive

- Crossfree cascadable

- Schmitt Trigger on the inputs

- 30 ns (typ.) glitch filter on every input

- High noise immunity

- Segment outputs short circuit protected

- LCD blanking function

- - 40 to +85 °C temperature range

- On request extended temperature range,

40 to +125 °C

- QFP52 and TAB packages

# Description

The V 6108 is a CMOS integrated circuit that drives LCD. The circuit drives up to 40 LCD segments from a serial clocked input. It has a serial output for cascading to further drives. The serially clocked data is parallel loaded into 40 latches under control of the strobe pin. The latched data determines which segments are ON or OFF. Any segment output can be used to drive a backplane. A blank function is provided to clear the display.

# Applications

- Balances and scales

- Automotive displays

- Utility meters

- Large displays

- Pagers

- Portable, battery operated products

- Telephones

### **Typical Operating Configuration**

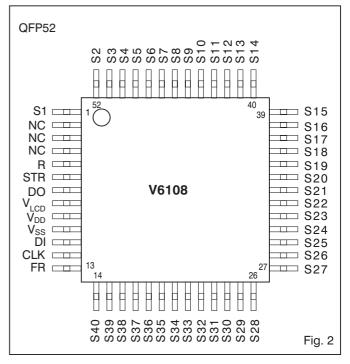

# Pin Assignment

Table 3

### Absolute Maximum Ratings

| Parameter                        | Symbol            | Conditions                     |

|----------------------------------|-------------------|--------------------------------|

| Logic supply voltage             | V <sub>DD</sub>   | -0.3V to +10V                  |

| LCD supply voltage <sup>1)</sup> | V <sub>LCD</sub>  | -0.3V to +14V                  |

| Voltage at DI, CLK,STR,          | VLOGIC            | -0.3V to V <sub>DD</sub> +0.3V |

| FR, R, DO                        | Loaio             |                                |

| Voltage at S1 to S40             | V <sub>DISP</sub> | $V_{DD}$ to $V_{LCD}$ + 0.3V   |

| Storage temperature range        | T <sub>STO</sub>  | - 65 to +150 °C                |

| Power dissipation                | P <sub>MAX</sub>  | 100 mW                         |

| Electrostatic discharge max. to  |                   |                                |

| MIL-STD-883 C method 3015        | V <sub>Smax</sub> | 1000V                          |

| Max. soldering conditions        | Τ <sub>s</sub>    | 250 °C x 10 s                  |

$^{\rm 1)}$  V\_{\rm LCD} has to be higher or equal to V\_{\rm DD} Table 1 Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

### **Electrical Characteristics**

$V_{\text{DD}}$  = 5V  $\pm$  10%,  $V_{\text{LCD}}$  = 12 V and  $T_{\text{A}}$  = -40 to 85 °C, unless otherwise specified

### **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range. Unused inputs must always be tied to a defined logic voltage level.

### **Operating Conditions**

| Parameter                           | Symbol           | Min.     | Тур. | Max. | Units |

|-------------------------------------|------------------|----------|------|------|-------|

| Operating temperature <sup>1)</sup> | T <sub>A</sub>   | -40      |      | +125 | °C    |

| Logic supply voltage                | V <sub>DD</sub>  | 2.0      |      | 8    | V     |

| LCD supply voltage                  | V <sub>LCD</sub> | $V_{DD}$ |      | 12   | V     |

<sup>1)</sup> The maximum operating temperature is confirmed Table 2 by sampling at initial device qualification. In production, all devices are tested at +85 °C. On request devices tested at +125°C can be supplied.

| Parameter                 | Symbol           | Test Conditions                                                                    | Min.                   | Тур. | Max.                  | Units |

|---------------------------|------------------|------------------------------------------------------------------------------------|------------------------|------|-----------------------|-------|

| Static supply current     | I <sub>DD</sub>  | See note <sup>1)</sup>                                                             |                        | 0.1  | 1                     | μA    |

| Static supply current     | I <sub>LCD</sub> | See note <sup>1)</sup>                                                             |                        | 0.1  | 1                     | μA    |

| Dynamic supply current    | I <sub>DD</sub>  | See note <sup>1)2)</sup>                                                           |                        | 55   | 75                    | μA    |

| Dynamic supply current    | I <sub>LCD</sub> | See note <sup>1)3)</sup>                                                           |                        | 0.6  | 5                     | μA    |

| All Input Signals         | 200              |                                                                                    |                        |      |                       |       |

| Low level input voltage   | VIL              |                                                                                    |                        |      | 0.8                   | V     |

| High level input voltage  | VIH              |                                                                                    | 3.8                    | 3.5  |                       | V     |

| Leakage Input current     |                  | $V_{IN} = V_{SS}$ or $V_{IN} = V_{DD}$                                             |                        |      | 1                     | μA    |

| Data Output DO            |                  |                                                                                    |                        |      |                       |       |

| High level output voltage | V <sub>OH</sub>  | $I_{\rm H} = 100 \mu {\rm A}  {\rm V}_{\rm DD} = {\rm V}_{\rm LCD} = 4.5  {\rm V}$ | V <sub>DD</sub> - 100  |      |                       | mV    |

| Low level output voltage  | V <sub>OL</sub>  | $I_{\rm L} = 100 \mu {\rm A}  {\rm V}_{\rm DD} = {\rm V}_{\rm LCD} = 4.5  {\rm V}$ | 55                     |      | $ V_{ss} + 100 $      | mV    |

| Driver Outputs S1S40      | 0L               |                                                                                    |                        |      |                       |       |

| High level output voltage | V <sub>SH</sub>  | $I_{\rm H} = 20 \mu \text{A}, V_{\rm DD} = V_{\rm LCD} = 4.5 \text{V}$             | V <sub>LCD</sub> - 100 |      |                       | mV    |

| Low level output voltage  | V <sub>SL</sub>  | $I_{L} = 20 \mu A, V_{DD} = V_{LCD} = 4.5 V$                                       | 202                    |      | V <sub>ss</sub> + 100 | mV    |

| Short Circuit Current     | I <sub>SC</sub>  | only one output                                                                    |                        | 0.9  | 2                     | mA    |

<sup>1)</sup> Tested with  $V_{IL} = V_{SS}$ ,  $V_{IH} = V_{DD}$ <sup>2)</sup> Tested with  $f_{CL} = 100$  kHz,  $F_{DI} = 50$  kHz, 50 pF on each segment <sup>3)</sup> Tested with  $f_{FL} = 64$  Hz,  $f_{CL} = 0$  Hz, 50 pF on each segment

### **Timing Characteristics**

$V_{\text{DD}}=5 \overline{V} \pm$  10%,  $V_{\text{LCD}}=$  12 V and  $T_{\text{A}}=$  -40 to +85°C, unless otherwise specified

| Parameter                                  | Symbol           | Test Conditions            | Min. | Тур.                | Max.            | Units   |

|--------------------------------------------|------------------|----------------------------|------|---------------------|-----------------|---------|

| Clock high pulse width                     | t <sub>CH</sub>  |                            | 500  |                     |                 | ns      |

| Clock low pulse width                      | t <sub>CL</sub>  |                            | 500  |                     |                 | ns      |

| Clock and FR rise time                     | t <sub>CR</sub>  |                            |      |                     | 500             | ns      |

| Clock and FR fall time                     | t <sub>CF</sub>  |                            |      |                     | 500             | ns      |

| Data input setup time                      | t <sub>DS</sub>  |                            | 250  |                     |                 | ns      |

| Data input hold time                       | t <sub>DH</sub>  |                            | 0    |                     |                 | ns      |

| Data output propagation                    | t <sub>PD</sub>  | $C_{LOAD} = 50 \text{ pF}$ |      | 600                 | 800             | ns      |

| CLK falling to STR rising                  | t <sub>P</sub>   |                            | 50   |                     |                 | ns      |

| STR falling to CLK falling                 | t <sub>D</sub>   |                            | 250  |                     |                 | ns      |

| STR pulse width                            | t <sub>STR</sub> |                            | 200  |                     |                 | ns      |

| FR frequency                               | f <sub>FR</sub>  |                            |      | 64 Hz <sup>1)</sup> | 1 <sup>2)</sup> | MHz     |

| Delay \$1 - \$40 fall time                 | t <sub>SF</sub>  |                            |      | 0.5                 | 1               | μs      |

| Delay S1 - S40 rise time                   | t <sub>SR</sub>  |                            |      | 2.9                 | 5               | μs      |

| <sup>1)</sup> Recommended frame frequency. | <sup>2)</sup> Ma | aximum test frequency.     |      |                     |                 | Table 4 |

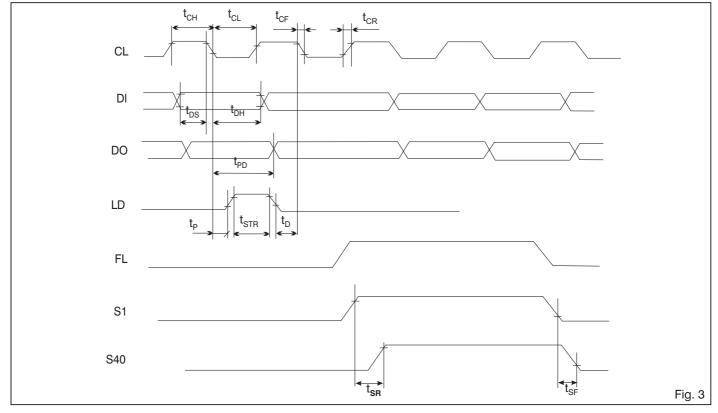

# **Timing Waveforms**

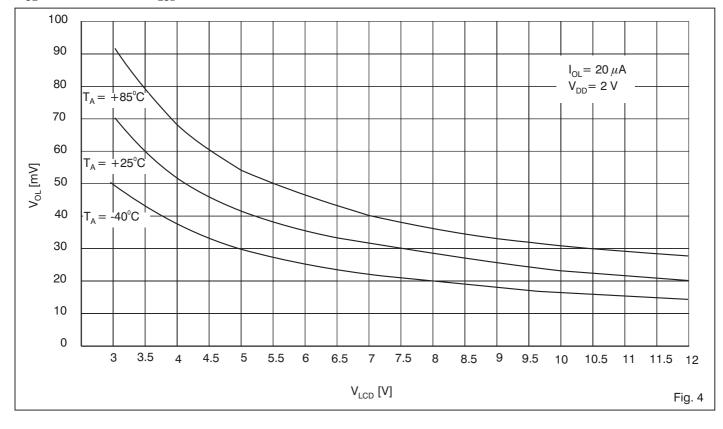

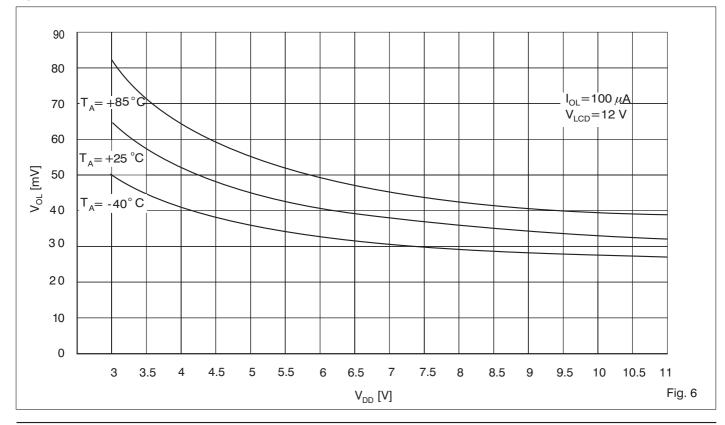

$V_{OL}\,S1$  ... S40 versus  $V_{LCD}$  at -40 °C, +25 °C and +85 °C

# V6108

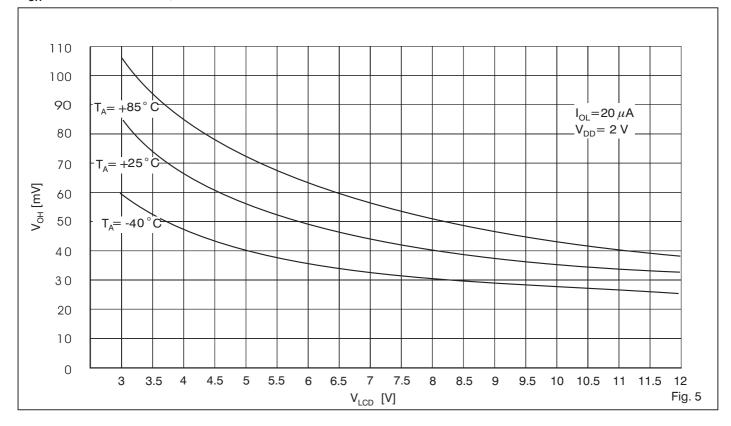

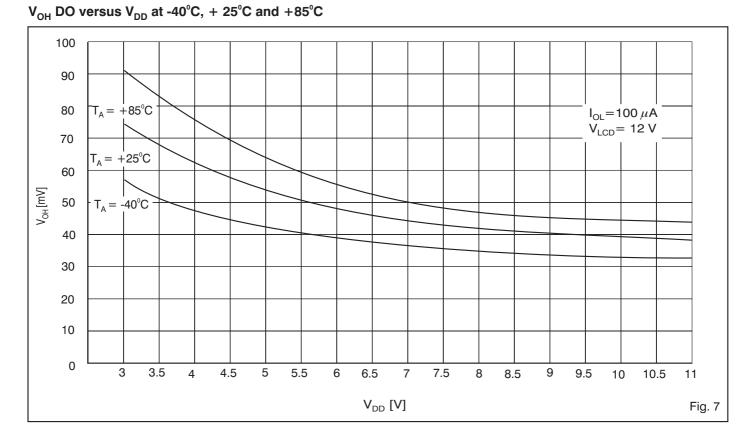

$V_{OH}$  S1 ... S40 versus  $V_{\mbox{\tiny LCD}}$  at – 40 °C, +25 °C and+85 °C

$V_{OL}$  DO versus  $V_{DD}$  at –  $40^{\circ}C,\,+25^{\circ}C$  and  $+85^{\circ}C$

V6108

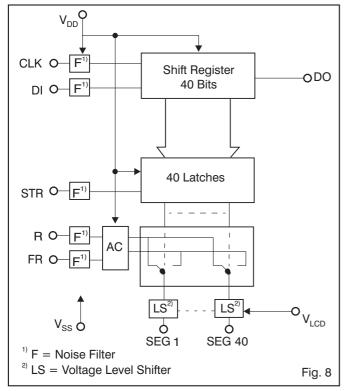

## **Block Diagram**

# **Pin Assignments**

| Name             | Function                               |

|------------------|----------------------------------------|

| S1S40            | Segment drive outputs                  |

| V <sub>LCD</sub> | Power supply for the LCD               |

| V <sub>DD</sub>  | Power supply for logic                 |

| FR               | Input for segment frequency control    |

| DI               | Serial data input                      |

| DO               | Serial data output                     |

| CLK              | Clock input                            |

| STR              | Strobes the input data into the output |

|                  | latches                                |

| R                | Display blank control input            |

| V <sub>SS</sub>  | Supply ground                          |

|                  | Table 5                                |

# **Functional Description**

### Supply Voltages $V_{\text{LCD}},\,V_{\text{DD}},\,V_{\text{SS}}$

$V_{\text{DD}}$  is the positive supply line for the logic and  $V_{\text{LCD}}$  for the display signals.  $V_{\text{LCD}}$  has to be equal or higher than  $V_{\text{DD}.}$  All voltages are specified relative to  $V_{\text{SS}}.$

### Data Input / Output (DI / DO)

The data input pin (DI) accepts serial data from the data source. The data is clocked in a rate determined by the clock input frequency (CLK). A logic "1" on DI corresponds to a visible segment when the backplane is driven by a signal corresponding to logic "0". The data at DO is equal to the data at DI delayed by 40 clock periods. In

order to cascade devices the DO of one chip must be connected to DI of the following chip (see Fig. 1).

#### **CLK Input**

The clock input pin (CLK) is used to clock the DI serial data into the 40-bit shift register. Loading, shifting and outputting of the data occurs at the falling edge of this clock (see Fig. 3). When cascading devices, all CLK lines should be tied together.

#### **STR Input**

The strobe input pin (STR) is used to latch the input data shifted into the 40-bit shift register. The latched data is held for display. A logic "1" on the STR input transfers the data contained in the shift register cells to the corresponding latches. The latches remain open during the whole time STR remains at logic "1". When cascading devices the STR lines should all be connected.

### **R** Input

When R is active (high), the display is blanked: all segment outputs are tied to  $V_{SS}$ . R does not clear the information in the latches.

#### **Segment Driver**

The number of segment drivers available on the chip is 40. Each segment driver can be used as backplane-driver. If two or more drivers are connected together, care must be taken to ensure the drivers do not cause circuit malfunction by driving one against the other.

#### **FR Input**

This input controls the segment output switching frequency according to Table 6. It must be connected to an external clock signal. When cascading devices, their FR inputs may all be connected to a common signal.

#### Segment Switching Table

| Latched Signal (DI)<br>$0 = V_{IL}$ $1 = V_{IH}$ | Signal<br>FR | Segment Voltage<br>$0 = V_{SS}$ $1 = V_{LCD}$ |

|--------------------------------------------------|--------------|-----------------------------------------------|

| 0                                                | 0            | 0                                             |

| 0                                                | 1            | 1                                             |

| 1                                                | 0            | 1                                             |

| 1                                                | 1            | 0                                             |

Table 6

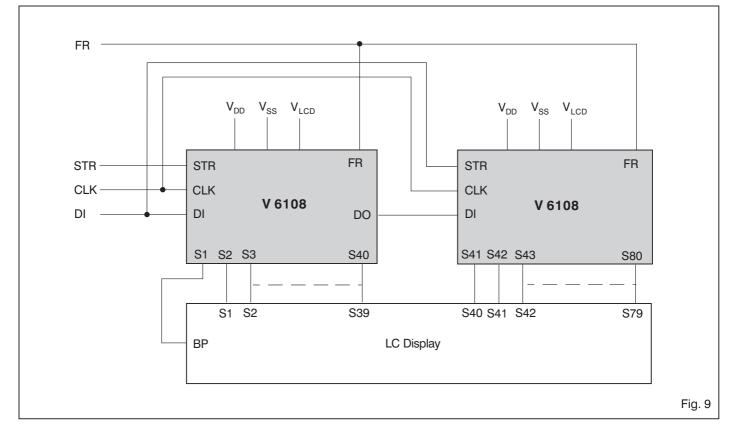

# Typical Applications

Type V 6108 Circuits Driving an 79 Segment Display

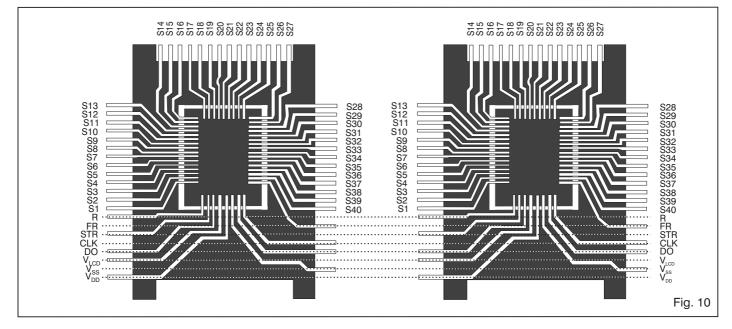

### **Cascaded V6108 TAB for Direct Drive Application**

## Package and Ordering Information

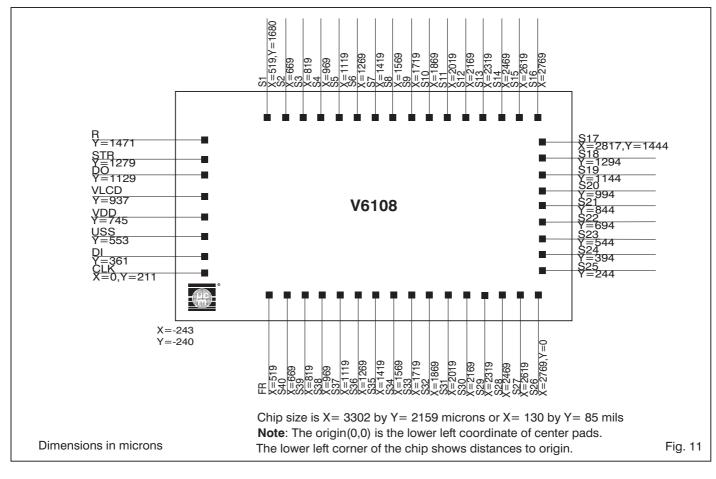

**Dimensions of Chip Form**

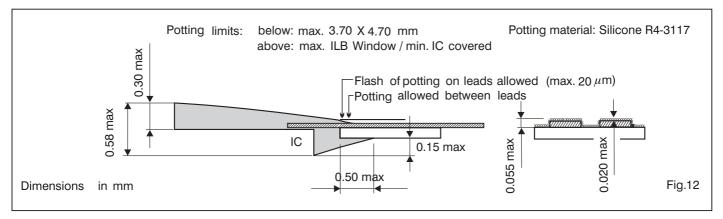

#### Side View and Recommended Solder Area

#### **Ordering Information**

When ordering, please specify the complete Part Number.

| Part Number | Package / Die Form                   | Delivery Form<br>/ Bumping | Package<br>Marking |  |

|-------------|--------------------------------------|----------------------------|--------------------|--|

| V6108QF52D  | QFP52, pin plastic package           | Tray                       | V6108_52FI         |  |

| V6108WS11   | Sawn wafer, 11 mils thickness        | No bumps                   | N/A                |  |

| V6108WP11   | Die in wafle pack, 11 mils thickness | No bumps                   | N/A                |  |

| V6108WP11E  | Die in wafle pack, 11 mils thickness | With gold bumps            | N/A                |  |

| V6108TBB    | TAB (Tape Automated Bonding), film B | -                          | N/A                |  |

EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.

© 2002 EM Microelectronic-Marin SA, 03/02, Rev. C/431

EM MICROELECTRONIC-MARIN SA, CH-2074 Marin, Switzerland, Tel. +41 - (0)32 75 5 111, Fax +41 - (0)32 75 55 403