Data sheet acquired from Harris Semiconductor SCHS198A

November 1997 - Revised May 2000

# High Speed CMOS Logic Dual 4-Stage Static Shift Register

#### Features

- Maximum Frequency, Typically 60MHz

C<sub>L</sub> = 15pF, V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C

- · Positive-Edge Clocking

- Overriding Reset

- · Buffered Inputs and Outputs

- Fanout (Over Temperature Range)

- Wide Operating Temperature Range ...-55°C to 125°C

- Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity:  $N_{IL}$  = 30%,  $N_{IH}$  = 30% of  $V_{CC}$  at  $V_{CC}$  = 5V

## Description

The 'HC4015 consists of two identical, independent, 4-stage serial-input/parallel-output registers. Each register has independent Clock (CP) and Reset (MR) inputs as well as a single serial Data input. "Q" outputs are available from each of the four stages on both registers. All register stages are D-type, master-slave flip-flops. The logic level present at the Data input is transferred into the first register stage and shifted over one stage at each positive- going clock transition. Resetting of all stages is accomplished by a high level on the reset line.

The device can drive up to 10 low power Schottky equivalent loads. The 'HC4015 is an enhanced version of equivalent CMOS types.

## **Ordering Information**

| PART NUMBER   | TEMP. RANGE (°C) | PACKAGE      |  |  |

|---------------|------------------|--------------|--|--|

| CD54HC4015F3A | -55 to 125       | 16 Ld CERDIP |  |  |

| CD74HC4015E   | -55 to 125       | 16 Ld PDIP   |  |  |

#### **NOTES**

- 1. When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

- Wafer or die for this part number is available which meets all electrical specifications. Please contact your local TI sales office or customer service for ordering information.

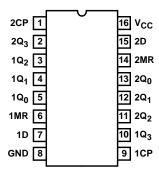

## **Pinout**

CD54HC4015 (CERDIP) CD74HC4015 (PDIP) TOP VIEW

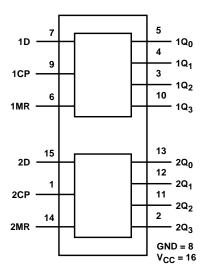

# Functional Diagram

#### **TRUTH TABLE**

|              | INPUTS |   | OUTPUTS        |                 |                 |                 |  |  |  |  |

|--------------|--------|---|----------------|-----------------|-----------------|-----------------|--|--|--|--|

| СР           | D      | R | Q <sub>0</sub> | Q <sub>1</sub>  | Q <sub>2</sub>  | $Q_3$           |  |  |  |  |

| 1            | I      | L | L              | q' <sub>0</sub> | <b>q</b> '1     | q' <sub>2</sub> |  |  |  |  |

| 1            | h      | L | Н              | q' <sub>0</sub> | q' <sub>1</sub> | q' <sub>2</sub> |  |  |  |  |

| $\downarrow$ | Х      | L | q'o            | q'1             | q'2             | q'3             |  |  |  |  |

| Х            | Х      | Н | L              | L               | L               | L               |  |  |  |  |

## NOTES:

H = High Voltage Level

h = High Voltage Level One Set-up Time Prior to the Low to High Clock Transition

L = Low Voltage Level

I = Low Voltage Level One Set-up Time Prior to the Low to High Clock Transition

X = Don't Care.

↑ = Low to High Clock Transition

$\downarrow$  = High to Low Clock Transition

$q_n' = L$ ower case letters indicate the state of the referenced output one set-up time prior to the Low to High clock transition.

#### CD54/74HC4015

#### **Absolute Maximum Ratings**

##

#### **Thermal Information**

| Thermal Resistance (Typical, Note 3)     | θ <sub>JA</sub> ( <sup>o</sup> C/W)     |

|------------------------------------------|-----------------------------------------|

| PDIP Package                             | 90                                      |

| Maximum Junction Temperature             |                                         |

| Maximum Storage Temperature Range        | 65 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s) | 300°C                                   |

| (SOIC - Lead Tips Only)                  |                                         |

|                                          |                                         |

#### **Operating Conditions**

| Temperature Range, T <sub>A</sub>                                                 |

|-----------------------------------------------------------------------------------|

| Supply Voltage Range, V <sub>CC</sub>                                             |

| HC Types2V to 6V                                                                  |

| DC Input or Output Voltage, V <sub>I</sub> , V <sub>O</sub> 0V to V <sub>CC</sub> |

| Input Rise and Fall Time                                                          |

| 2V                                                                                |

| 4.5V 500ns (Max)                                                                  |

| 6V                                                                                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

3.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## **DC Electrical Specifications**

|                                  |                                    | TES<br>CONDI                       |                     | V <sub>CC</sub> | 25°C |      |      | -40°C TO 85°C |      | -55°C TO 125°C |      |       |     |   |

|----------------------------------|------------------------------------|------------------------------------|---------------------|-----------------|------|------|------|---------------|------|----------------|------|-------|-----|---|

| PARAMETER                        | SYMBOL                             | V <sub>I</sub> (V)                 | I <sub>O</sub> (mA) | (V)             | MIN  | TYP  | MAX  | MIN           | MAX  | MIN            | MAX  | UNITS |     |   |

| High Level Input                 | V <sub>IH</sub>                    | -                                  | -                   | 2               | 1.5  | -    | -    | 1.5           | -    | 1.5            | -    | V     |     |   |

| Voltage                          |                                    |                                    |                     | 4.5             | 3.15 | -    | -    | 3.15          | -    | 3.15           | -    | V     |     |   |

|                                  |                                    |                                    |                     | 6               | 4.2  | -    | -    | 4.2           | -    | 4.2            | -    | V     |     |   |

| Low Level Input                  | V <sub>IL</sub>                    | -                                  | -                   | 2               | -    | -    | 0.5  | -             | 0.5  | -              | 0.5  | V     |     |   |

| Voltage                          |                                    |                                    |                     | 4.5             | -    | -    | 1.35 | -             | 1.35 | -              | 1.35 | V     |     |   |

|                                  |                                    |                                    |                     | 6               | -    | -    | 1.8  | -             | 1.8  | -              | 1.8  | V     |     |   |

| High Level Output                | V <sub>OH</sub>                    | $V_{\text{IH}}$ or $V_{\text{IL}}$ | -0.02               | 2               | 1.9  | -    | -    | 1.9           | -    | 1.9            | -    | V     |     |   |

| Voltage<br>CMOS Loads            |                                    |                                    | -0.02               | 4.5             | 4.4  | -    | -    | 4.4           | -    | 4.4            | -    | V     |     |   |

|                                  |                                    |                                    | -0.02               | 6               | 5.9  | -    | -    | 5.9           | -    | 5.9            | -    | V     |     |   |

| High Level Output                | 1                                  |                                    | -                   | -               | -    | -    | -    | -             | -    | -              | -    | V     |     |   |

| Voltage<br>TTL Loads             |                                    |                                    | -4                  | 4.5             | 3.98 | -    | -    | 3.84          | -    | 3.7            | -    | V     |     |   |

| TTE Education                    |                                    |                                    | -5.2                | 6               | 5.48 | -    | -    | 5.34          | -    | 5.2            | -    | V     |     |   |

| Low Level Output V <sub>OL</sub> | V <sub>IH</sub> or V <sub>IL</sub> | 0.02                               | 2                   | -               | -    | 0.1  | -    | 0.1           | -    | 0.1            | V    |       |     |   |

| Voltage<br>CMOS Loads            |                                    |                                    | 0.02                | 4.5             | -    | -    | 0.1  | -             | 0.1  | -              | 0.1  | V     |     |   |

| OWOO Eddas                       |                                    |                                    | 0.02                | 6               | -    | -    | 0.1  | -             | 0.1  | -              | 0.1  | V     |     |   |

| Low Level Output                 | 1                                  |                                    | -                   | -               | -    | -    | -    | -             | -    | -              | -    | V     |     |   |

| Voltage<br>TTL Loads             |                                    |                                    |                     |                 | 4    | 4.5  | -    | -             | 0.26 | -              | 0.33 | -     | 0.4 | V |

| TIL LOGUS                        |                                    | 5.2                                | 6                   | -               | -    | 0.26 | -    | 0.33          | -    | 0.4            | V    |       |     |   |

| Input Leakage<br>Current         | Ι <sub>Ι</sub>                     | V <sub>CC</sub> or<br>GND          | -                   | 6               | -    | -    | ±0.1 | -             | ±1   | -              | ±1   | μА    |     |   |

| Quiescent Device<br>Current      | Icc                                | V <sub>CC</sub> or<br>GND          | 0                   | 6               | -    | -    | 8    | -             | 80   | -              | 160  | μА    |     |   |

NOTE: For dual-supply systems theoretical worst case ( $V_I$  = 2.4V,  $V_{CC}$  = 5.5V) specification is 1.8mA.

## CD54/74HC4015

## **Prerequisite for Switching Specifications**

|                   |                  |                     | 25°C -40°C TO 85°C |     | -55°C T |     |     |     |       |

|-------------------|------------------|---------------------|--------------------|-----|---------|-----|-----|-----|-------|

| PARAMETER         | SYMBOL           | V <sub>CC</sub> (V) | MIN                | MAX | MIN     | MAX | MIN | MAX | UNITS |

| Maximum Clock     | f <sub>MAX</sub> | 2                   | 6                  | -   | 5       | -   | 4   | -   | MHz   |

| Frequency         |                  | 4.5                 | 30                 | -   | 24      | -   | 20  | -   | MHz   |

|                   |                  | 6                   | 35                 | -   | 28      | -   | 24  | -   | MHz   |

| Clock Pulse Width | t <sub>W</sub>   | 2                   | 80                 | -   | 100     | -   | 120 | -   | ns    |

|                   |                  | 4.5                 | 16                 | -   | 20      | -   | 24  | -   | ns    |

|                   |                  | 6                   | 14                 | -   | 17      | -   | 20  | -   | ns    |

| MR Pulse Width    | t <sub>W</sub>   | 2                   | 150                | -   | 190     | -   | 225 | -   | ns    |

|                   |                  | 4.5                 | 30                 | -   | 38      | -   | 45  | -   | ns    |

|                   |                  | 6                   | 26                 | -   | 33      | -   | 38  | -   | ns    |

| MR Recovery Time  | tREC             | 2                   | 50                 | -   | 65      | -   | 75  | -   | ns    |

|                   |                  | 4.5                 | 10                 | -   | 13      | -   | 15  | -   | ns    |

|                   |                  | 6                   | 9                  | -   | 11      | -   | 13  | -   | ns    |

| Set-up Time,      | tsul, tsuh       | 2                   | 60                 | -   | 75      | -   | 90  | -   | ns    |

| Data-In to CP     |                  | 4.5                 | 12                 | -   | 15      | -   | 18  | -   | ns    |

|                   |                  | 6                   | 10                 | -   | 13      | -   | 15  | -   | ns    |

| Hold Time,        | tH               | 2                   | 0                  | -   | 0       | -   | 0   | -   | ns    |

| Data-In to CP     |                  | 4.5                 | 0                  | -   | 0       | -   | 0   | -   | ns    |

|                   |                  | 6                   | 0                  | -   | 0       | -   | 0   | -   | ns    |

## **Switching Specifications** Input $t_r$ , $t_f = 6ns$

|                                                  | TEST                                  |                       | V <sub>CC</sub> | 25°C |     |     | -40°C TO 85°C |     | -55°C TO 125°C |     |       |

|--------------------------------------------------|---------------------------------------|-----------------------|-----------------|------|-----|-----|---------------|-----|----------------|-----|-------|

| PARAMETER                                        | SYMBOL                                | CONDITIONS            |                 | MIN  | TYP | MAX | MIN           | MAX | MIN            | MAX | UNITS |

| Propagation Delay (Figure 1)                     | t <sub>PLH,</sub>                     | C <sub>L</sub> = 50pF | 2               | -    | -   | 175 | -             | 220 | -              | 270 | ns    |

| Clock to Q <sub>n</sub>                          | t <sub>PHL</sub>                      |                       | 4.5             | -    | -   | 35  | -             | 44  | -              | 54  | ns    |

|                                                  |                                       | C <sub>L</sub> =15pF  | 5               | -    | 14  | -   | -             | -   | -              | -   | ns    |

|                                                  |                                       | C <sub>L</sub> = 50pF | 6               | -    | -   | 30  | -             | 37  | -              | 46  | ns    |

| MR to Q <sub>n</sub> , (Clock High)              | t <sub>PLH</sub> ,                    | C <sub>L</sub> = 50pF | 2               | -    | -   | 275 | -             | 345 | -              | 415 | ns    |

|                                                  | t <sub>PHL</sub>                      |                       | 4.5             | -    | -   | 55  | -             | 64  | -              | 83  | ns    |

|                                                  |                                       | C <sub>L</sub> =15pF  |                 |      | 25  | -   | -             | -   | -              | -   | ns    |

|                                                  |                                       | C <sub>L</sub> = 50pF | 6               | -    | -   | 47  | -             | 54  | -              | 71  | ns    |

| MR to Q <sub>n</sub> , (Clock Low)               | <sup>t</sup> PLH,<br><sup>t</sup> PHL | C <sub>L</sub> = 50pF | 2               | -    | -   | 325 | -             | 400 | -              | 490 | ns    |

|                                                  |                                       |                       | 4.5             | -    | -   | 65  | -             | 81  | -              | 98  | ns    |

|                                                  |                                       | C <sub>L</sub> =15pF  |                 |      | 25  | -   | -             | -   | -              | -   | ns    |

|                                                  |                                       | C <sub>L</sub> = 50pF | 6               | -    | -   | 55  | -             | 69  | -              | 83  | ns    |

| Output Transition Time                           | t <sub>TLH</sub> , t <sub>THL</sub>   | C <sub>L</sub> = 50pF | 2               | -    | -   | 75  | -             | 95  | -              | 110 | ns    |

| (Figure 1)                                       |                                       |                       | 4.5             | -    | -   | 15  | -             | 19  | -              | 22  | ns    |

|                                                  |                                       |                       | 6               | -    | -   | 13  | -             | 16  | -              | 19  | ns    |

| Input Capacitance                                | C <sub>IN</sub>                       | C <sub>L</sub> = 50pF | -               | -    | -   | 10  | -             | 10  | -              | 10  | pF    |

| Maximum Clock Frequency                          | f <sub>MAX</sub>                      | C <sub>L</sub> =15pF  | 5               | -    | 60  | -   | -             | -   | -              | -   | MHz   |

| Power Dissipation<br>Capacitance<br>(Notes 4, 5) | C <sub>PD</sub>                       | C <sub>L</sub> =15pF  | 5               | -    | 43  | -   | -             | -   | -              | -   | pF    |

## NOTES:

- 4.  $C_{PD}$  is used to determine the dynamic power consumption, per shift register.

5.  $P_D = V_{CC}^2 f_i + \sum C_L V_{CC}^2$  where  $f_i$  = Input Frequency,  $C_L$  = Output Load Capacitance,  $V_{CC}$  = Supply Voltage.

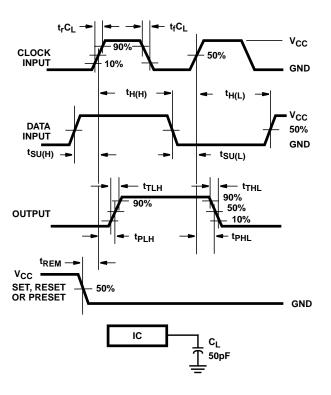

# Test Circuit and Waveform

FIGURE 1. HC SETUP TIMES, HOLD TIMES, REMOVAL TIME, AND PROPAGATION DELAY TIMES FOR EDGE TRIGGERED SEQUENTIAL LOGIC CIRCUITS

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated