# TEXAS INSTRUMENTS

Data sheet acquired from Harris Semiconductor SCHS205C

# CD54/74HC4049, CD54/74HC4050

**High-Speed CMOS Logic**

#### February 1998 - Revised March 2002

# Features

- Typical Propagation Delay: 6ns at  $V_{CC}$  = 5V,  $C_L$  = 15pF,  $T_A$  = 25<sup>o</sup>C

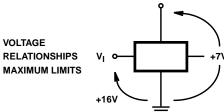

- High-to-Low Voltage Level Converter for up to V<sub>I</sub> = 16V

- Fanout (Over Temperature Range)

- Standard Outputs ..... 10 LSTTL Loads

- Bus Driver Outputs ..... 15 LSTTL Loads

- Wide Operating Temperature Range ... –55°C to 125°C

- · Balanced Propagation Delay and Transition Times

- Significant Power Reduction Compared to LSTTL Logic ICs

- HC Types

- 2V to 6V Operation

- High Noise Immunity: N<sub>IL</sub> = 30%, N<sub>IH</sub> = 30% of V<sub>CC</sub> at V<sub>CC</sub> = 5V

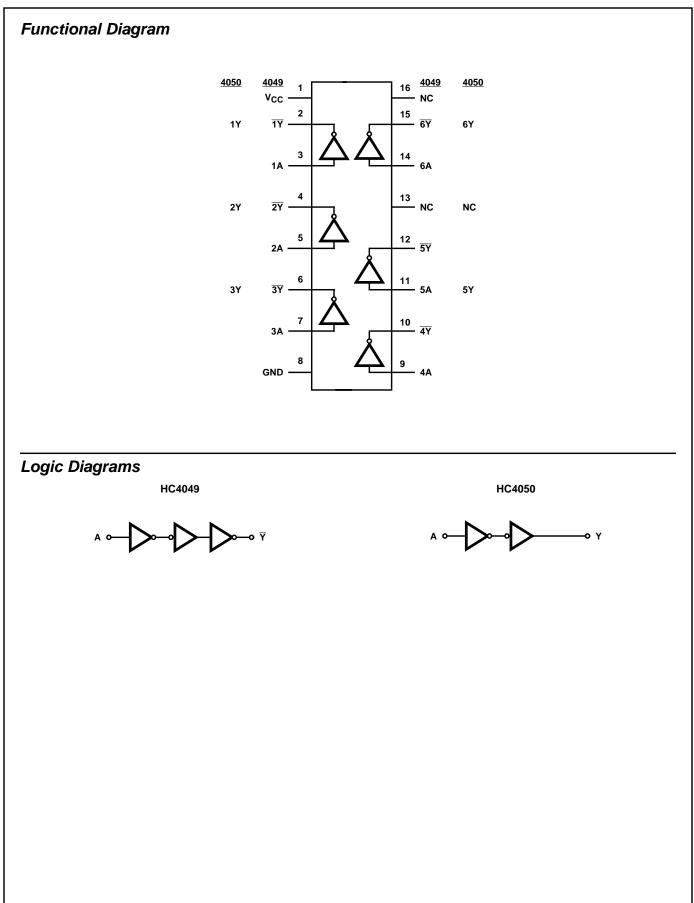

# Description

The 'HC4049 and 'HC4050 are fabricated with high-speed silicon gate technology. They have a modified input protection structure that enables these parts to be used as logic level translators which convert high-level logic to a low-level logic while operating off the low-level logic supply. For example, 15-V input pulse levels can be down-converted to 0-V to 5-V logic levels. The modified input protection structure protects the input from negative electrostatic

discharge. These parts also can be used as simple buffers or inverters without level translation. The 'HC4049 and 'HC4050 are enhanced versions of equivalent CMOS types.

Hex Buffers, Inverting and Non-Inverting

# **Ordering Information**

| PART NUMBER   | TEMP. RANGE<br>( <sup>o</sup> C) | PACKAGE      |

|---------------|----------------------------------|--------------|

| CD54HC4049F3A | -55 to 125                       | 16 Ld CERDIP |

| CD74HC4049E   | -55 to 125                       | 16 Ld PDIP   |

| CD74HC4049M   | -55 to 125                       | 16 Ld SOIC   |

| CD74HC4049NSR | -55 to 125                       | 16 Ld SOP    |

| CD54HC4050F3A | -55 to 125                       | 16 Ld CERDIP |

| CD74HC4050E   | -55 to 125                       | 16 Ld PDIP   |

| CD74HC4050M   | -55 to 125                       | 16 Ld SOIC   |

| CD74HC4050NSR | -55 to 125                       | 16 Ld SOP    |

| CD74HC4050PW  | -55 to 125                       | 16 Ld TSSOP  |

NOTES:

- When ordering, use the entire part number. Add the suffix 96 to the M suffix or the R suffix to the PW package to obtain the variant in the tape and reel.

- 2. Wafer and die is available which meets all electrical specifications. Please contact your local TI sales office or customer service for ordering information.

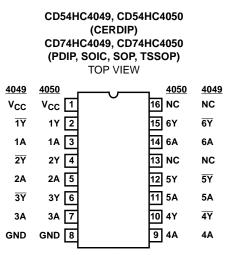

## Pinout

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © 2002, Texas Instruments Incorporated

#### **Absolute Maximum Ratings**

| DC Supply Voltage, V <sub>CC</sub> 0.5V to 7V                                   |

|---------------------------------------------------------------------------------|

| DC Input Diode Current, IIK                                                     |

| For $V_I < -0.5V$ or $V_I > V_{CC} + 0.5V$                                      |

| DC Output Diode Current, I <sub>OK</sub>                                        |

| For $V_O < -0.5V$ or $V_O > V_{CC} + 0.5V\pm 20$ mA                             |

| DC Output Source or Sink Current per Output Pin, IO                             |

| For $V_{O} > -0.5V$ or $V_{O} < V_{CC} + 0.5V\pm 25$ mA                         |

| DC V <sub>CC</sub> or Ground Current, I <sub>CC or</sub> I <sub>GND</sub> ±50mA |

|                                                                                 |

| Operating Conditions                                                            |

####

## **Thermal Information**

| Package Thermal Impedance, $\theta_{JA}$ (see Note 3):       |

|--------------------------------------------------------------|

| PDIP Package                                                 |

| SOIC Package                                                 |

| SOP Package 64°C/W                                           |

| TSSOP Package 108°C/W                                        |

| Maximum Junction Temperature (Hermetic Package or Die) 175°C |

| Maximum Junction Temperature (Plastic Package) 150°C         |

| Maximum Storage Temperature Range65°C to 150°C               |

| Maximum Lead Temperature (Soldering 10s)                     |

| (SOIC - Lead Tips Only)                                      |

| V <sub>CC</sub>                                              |

|                                                              |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

3. The package thermal impedance is calculated in accordance with JESD 51-7.

### **DC Electrical Specifications**

| PARAMETER                                   |                 | TEST<br>CONDITIONS                                 |                     | Vcc | 25 <sup>0</sup> C |     |      | -40°C 1 | го 85°С | –55 <sup>0</sup> C TO<br>125 <sup>0</sup> C |      |       |

|---------------------------------------------|-----------------|----------------------------------------------------|---------------------|-----|-------------------|-----|------|---------|---------|---------------------------------------------|------|-------|

|                                             | SYMBOL          | V <sub>I</sub> (V)                                 | I <sub>O</sub> (mA) | (V) | MIN               | TYP | MAX  | MIN     | MAX     | MIN                                         | MAX  | UNITS |

| HC TYPES                                    |                 |                                                    |                     |     |                   |     |      |         |         |                                             |      | -     |

| High Level Input V <sub>IH</sub><br>Voltage | VIH             | -                                                  | -                   | 2   | 1.5               | -   | -    | 1.5     | -       | 1.5                                         | -    | V     |

|                                             |                 |                                                    |                     | 4.5 | 3.15              | -   | -    | 3.15    | -       | 3.15                                        | -    | V     |

|                                             |                 |                                                    |                     | 6   | 4.2               | -   | -    | 4.2     | -       | 4.2                                         | -    | V     |

| Low Level Input                             | VIL             | -                                                  | -                   | 2   | -                 | -   | 0.5  | -       | 0.5     | -                                           | 0.5  | V     |

| Voltage                                     |                 |                                                    |                     | 4.5 | -                 | -   | 1.35 | -       | 1.35    | -                                           | 1.35 | V     |

|                                             |                 |                                                    |                     | 6   | -                 | -   | 1.8  | -       | 1.8     | -                                           | 1.8  | V     |

| High Level Output<br>Voltage<br>CMOS Loads  | VOH             | V <sub>OH</sub> V <sub>IH</sub> or V <sub>IL</sub> | -0.02               | 2   | 1.9               | -   | -    | 1.9     | -       | 1.9                                         | -    | V     |

|                                             |                 |                                                    | -0.02               | 4.5 | 4.4               | -   | -    | 4.4     | -       | 4.4                                         | -    | V     |

|                                             |                 |                                                    | -0.02               | 6   | 5.9               | -   | -    | 5.9     | -       | 5.9                                         | -    | V     |

| High Level Output                           | 7               |                                                    | -4                  | 4.5 | 3.98              | -   | -    | 3.84    | -       | 3.7                                         | -    | V     |

| Voltage<br>TTL Loads                        |                 |                                                    | -5.2                | 6   | 5.48              | -   | -    | 5.34    | -       | 5.2                                         | -    | V     |

| Low Level Output<br>Voltage<br>CMOS Loads   | V <sub>OL</sub> | $V_{IH}$ or $V_{IL}$                               | 0.02                | 2   | -                 | -   | 0.1  | -       | 0.1     | -                                           | 0.1  | V     |

|                                             |                 |                                                    | 0.02                | 4.5 | -                 | -   | 0.1  | -       | 0.1     | -                                           | 0.1  | V     |

|                                             |                 |                                                    | 0.02                | 6   | -                 | -   | 0.1  | -       | 0.1     | -                                           | 0.1  | V     |

| Low Level Output                            |                 |                                                    | 4                   | 4.5 | -                 | -   | 0.26 | -       | 0.33    | -                                           | 0.4  | V     |

| Voltage<br>TTL Loads                        | ě l             |                                                    | 5.2                 | 6   | -                 | -   | 0.26 | -       | 0.33    | -                                           | 0.4  | V     |

| Input Leakage<br>Current                    | lı              | V <sub>CC</sub> or<br>GND                          | -                   | 6   | -                 | -   | ±0.1 | -       | ±1      | -                                           | ±1   | μA    |

|                                             |                 | 15                                                 | -                   | 6   | -                 | -   | ±0.5 | -       | ±5      | -                                           | ±5   |       |

| Quiescent Device<br>Current                 | ICC             | V <sub>CC</sub> or<br>GND                          | 0                   | 6   | -                 | -   | 2    | -       | 20      | -                                           | 40   | μA    |

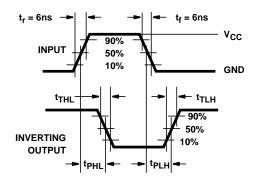

#### Switching Specifications Input tr, tf = 6ns

|                                                          | SYMBOL                              | TEST<br>CONDITIONS    |                     | 25 <sup>0</sup> C |     |     | –40 <sup>0</sup> С ТО<br>85 <sup>0</sup> С |     | –55 <sup>0</sup> C TO<br>125 <sup>0</sup> C |     |       |

|----------------------------------------------------------|-------------------------------------|-----------------------|---------------------|-------------------|-----|-----|--------------------------------------------|-----|---------------------------------------------|-----|-------|

| PARAMETER                                                |                                     |                       | V <sub>CC</sub> (V) | MIN               | TYP | MAX | MIN                                        | MAX | MIN                                         | MAX | UNITS |

| HC TYPES                                                 |                                     |                       |                     |                   |     |     |                                            |     |                                             | _   | -     |

| Propagation Delay,<br>nA to nY HC4049<br>nA to nY HC4050 | t <sub>PLH</sub> , t <sub>PHL</sub> | $C_L = 50 pF$         | 2                   | -                 | -   | 85  | -                                          | 105 | -                                           | 130 | ns    |

|                                                          |                                     |                       | 4.5                 | -                 | -   | 17  | -                                          | 21  | -                                           | 26  | ns    |

|                                                          |                                     |                       | 6                   | -                 | -   | 14  | -                                          | 18  | -                                           | 22  | ns    |

|                                                          |                                     | C <sub>L</sub> = 15pF | 5                   | -                 | 6   | -   | -                                          | -   | -                                           | -   | ns    |

| Transition Times (Figure 1)                              | t <sub>TLH</sub> , t <sub>THL</sub> | $C_L = 50 pF$         | 2                   | -                 | -   | 75  | -                                          | 95  | -                                           | 110 | ns    |

|                                                          |                                     |                       | 4.5                 | -                 | -   | 15  | -                                          | 19  | -                                           | 22  | ns    |

|                                                          |                                     |                       | 6                   | -                 | -   | 13  | -                                          | 16  | -                                           | 19  | ns    |

| Input Capacitance                                        | C <sub>I</sub>                      | -                     | -                   | -                 | -   | 10  | -                                          | 10  | -                                           | 10  | pF    |

| Power Dissipation Capacitance<br>(Notes 4, 5)            | C <sub>PD</sub>                     | -                     | 5                   | -                 | 35  | -   | -                                          | -   | -                                           | -   | pF    |

NOTES:

4. C<sub>PD</sub> is used to determine the dynamic power consumption, per gate.

5.  $P_D = V_{CC}^2 f_i (C_{PD} + C_L)$  where  $f_i$  = Input Frequency,  $C_L$  = Output Load Capacitance,  $V_{CC}$  = Supply Voltage.

# Test Circuit and Waveform

FIGURE 1. HC AND HCU TRANSITION TIMES AND PROPAGATION DELAY TIMES, COMBINATION LOGIC

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated