# AD7523, AD7533

December 1993

# Features

- 8, 9 and 10-Bit Linearity

- Low Gain and Linearity Temperature Coefficients

- Full Temperature Range Operation

- Static Discharge Input Protection

- TTL/CMOS Compatible

- +5V to +15V Supply Range

- Fast Settling Time: 150ns Max at +25°C

- Four Quadrant Multiplication

- AD7533 Direct AD7520 Equivalent

# Description

The AD7523 and AD7533 monolithic, low cost, high performance, 8-bit and 10-bit accurate, multiplying digital-to-analog converter (DAC), in a 16 pin DIP.

8-Bit Multiplying D/A Converters

Harris' thin film resistors on CMOS circuitry provide 10-bit resolution (8, 9 and 10-bit accuracy), with TTL/CMOS compatible operation.

The AD7523 and AD7533s accurate four quadrant multiplication, full military temperature range operation, full input protection from damage due to static discharge by clamps to V+ and GND, and very low power dissipation make it a very versatile converter.

Low noise audio gain controls, motor speed controls, digitally controlled gain and digital attenuators are a few of the wide range of applications of the AD7523 and AD7533.

# **Ordering Information**

| PART NUMBER        | NONLINEARITY   | TEMPERATURE RANGE | PACKAGE             |

|--------------------|----------------|-------------------|---------------------|

| AD7523JN, AD7533JN | 0.2% (8-Bit)   | 0°C to +70°C      | 16 Lead Plastic DIP |

| AD7523KN, AD7533KN | 0.1% (9-Bit)   | 0°C to +70°C      | 16 Lead Plastic DIP |

| AD7523LN, AD7533LN | 0.05% (10-Bit) | 0°C to +70°C      | 16 Lead Plastic DIP |

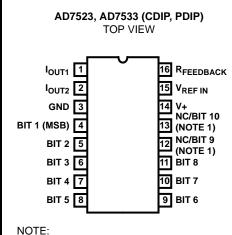

# Pinout

1. NC for AD7523 only.

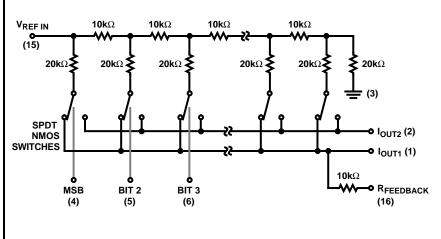

# Functional Block Diagram

Switches shown for digital inputs "High"

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright © Harris Corporation 1993

## **Absolute Maximum Ratings**

## **Thermal Information**

| Supply Voltage (V+ to GND)+17V         | Thermal Resistance $	heta_{JA}$ |

|----------------------------------------|---------------------------------|

| V <sub>REF</sub>                       | Plastic DIP Package 100°C/W     |

| Digital Input Voltage RangeV+ to GND   | Operating Temperature           |

| Output Voltage Compliance100mV to V+   | JN, KN, LN Versions             |

| Storage Temperature                    |                                 |

| Lead Temperature (Soldering 10s)+300°C |                                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **Electrical Specifications** $V_{+} = +15V$ , $V_{REF} = +10V$ , $V_{OUT1} = V_{OUT2} = 0V$ , Unless Otherwise Specified

|                                           |                                                                                                         |                                                                                   | AD7523               |          |                        |       |                      |        |                        |             |                               |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|----------|------------------------|-------|----------------------|--------|------------------------|-------------|-------------------------------|

| PARAMETER                                 |                                                                                                         | TEST CONDITIONS                                                                   | T <sub>A</sub> +25°C |          | T <sub>A</sub> MIN-MAX |       | T <sub>A</sub> +25°C |        | T <sub>A</sub> MIN-MAX |             |                               |

|                                           |                                                                                                         |                                                                                   | MIN                  | MAX      | MIN                    | МАХ   | MIN                  | МАХ    | MIN                    | МАХ         | UNITS                         |

| SYSTEM PERFORMA                           | NCE                                                                                                     |                                                                                   |                      |          |                        |       |                      |        |                        |             |                               |

| Resolution                                |                                                                                                         |                                                                                   | 8                    | -        | 8                      | -     | 10                   | -      | 10                     | -           | Bits                          |

| Nonlinearity J                            | $\label{eq:V_REF} \begin{array}{l} -10V \leq V_{REF} \leq +10V \\ V_{OUT1} = V_{OUT2} = 0V \end{array}$ | -                                                                                 | ±0.2                 | -        | ±0.2                   | -     | ±0.2                 | -      | ±0.2                   | % of<br>FSR |                               |

|                                           | К, Т                                                                                                    | (Note 1, 2, 5)                                                                    | -                    | ±0.1     | -                      | ±0.1  | -                    | ±0.1   | -                      | ±0.1        | % of<br>FSR                   |

|                                           | L                                                                                                       |                                                                                   | -                    | ±0.05    | -                      | ±0.05 | -                    | ±0.05  | -                      | ±0.05       | % of<br>FSR                   |

| Monotonicity                              |                                                                                                         |                                                                                   | Guaranteed           |          |                        |       | Guaranteed           |        |                        |             |                               |

| Gain Error                                |                                                                                                         | All Digital Inputs High<br>(Note 2)                                               | -                    | ±1.5     | -                      | ±1.8  | -                    | ±1.4   | -                      | ±1.8        | % of<br>FSR                   |

| Nonlinearity Tempco                       |                                                                                                         | $-10V \le V_{REF} \le +10V$<br>(Notes 2, 3)                                       | -                    | ±2       | -                      | ±2    | -                    | ±2     | -                      | ±2          | ppm of<br>FSR/ºC              |

| Gain Error Tempco                         |                                                                                                         |                                                                                   | -                    | ±10      | -                      | ±10   | -                    | ±10    | -                      | ±10         | ppm of<br>FSR/ <sup>o</sup> C |

| Output Leakage Current<br>(Either Output) |                                                                                                         | $V_{OUT1} = V_{OUT2} = 0$                                                         | -                    | ±50      | -                      | ±200  | -                    | ±50    | -                      | ±200        | nA                            |

| DYNAMIC CHARACTE                          | RISTICS                                                                                                 | 6                                                                                 |                      |          |                        |       |                      |        |                        |             |                               |

| Power Supply Rejectio                     | n                                                                                                       | V+ = 14.0V to 15.0V<br>(Note 2)                                                   | -                    | ±0.02    | -                      | ±0.03 | -                    | ±0.005 | -                      | ±0.008      | % of<br>FSR/%<br>of ∆V+       |

| Output Current Settling                   | I Time                                                                                                  | To 0.2% of FSR,<br>$R_L = 100\Omega$ (Note 3)                                     | -                    | 150      | -                      | 200   | -                    | 600    | -                      | 800         | ns                            |

| Feedthrough Error                         |                                                                                                         | V <sub>REF</sub> = 20Vpp, 200kHz<br>Sine Wave, All Digital<br>Inputs Low (Note 3) | -                    | ±1/2     | -                      | ±1    | -                    | ±0.05  | -                      | ±0.1        | LSB                           |

| REFERENCE INPUTS                          |                                                                                                         | •                                                                                 |                      | <u>n</u> |                        |       |                      |        |                        |             |                               |

| Input Resistance (Pin 2                   | 15)                                                                                                     | All Digital Inputs High<br>I <sub>OUT1</sub> at Ground (Note 3)                   | 5                    | -        | 5                      | -     | 5                    | -      | 5                      | -           | kΩ                            |

|                                           |                                                                                                         |                                                                                   | -                    | 20       | -                      | 20    | -                    | 20     | -                      | 20          | kΩ                            |

| Temperature Coefficien                    | nt                                                                                                      |                                                                                   | -                    | -500     | -                      | -500  | -                    | -300   | -                      | -300        | ppm/ºC                        |

|                                                              |                   |                                                                 | AD7523               |     |                        |                      | AD7533               |     |                        |          |       |

|--------------------------------------------------------------|-------------------|-----------------------------------------------------------------|----------------------|-----|------------------------|----------------------|----------------------|-----|------------------------|----------|-------|

|                                                              |                   |                                                                 | T <sub>A</sub> +25°C |     | T <sub>A</sub> MIN-MAX |                      | T <sub>A</sub> +25°C |     | T <sub>A</sub> MIN-MAX |          |       |

| PARAMETER                                                    |                   | TEST CONDITIONS                                                 | MIN                  | MAX | MIN                    | MAX                  | MIN                  | MAX | MIN                    | MAX      | UNITS |

| ANALOG OUTPUT                                                |                   |                                                                 |                      |     |                        |                      |                      |     |                        |          |       |

| Output Capacitance                                           | C <sub>OUT1</sub> | All Digital Inputs High                                         | -                    | 100 | -                      | 100                  | -                    | 100 | -                      | 100      | pF    |

|                                                              | C <sub>OUT2</sub> | (Note 3)                                                        | -                    | 30  | -                      | 30                   | -                    | 35  | -                      | 35       | pF    |

|                                                              | C <sub>OUT1</sub> | All Digital Inputs Low                                          | -                    | 30  | -                      | 30                   | -                    | 35  | -                      | 35       | pF    |

|                                                              | C <sub>OUT2</sub> | (Note 3)                                                        | -                    | 100 | -                      | 100                  | -                    | 100 | -                      | 100      | pF    |

| DIGITAL INPUTS                                               |                   |                                                                 |                      |     |                        |                      |                      |     |                        |          |       |

| Low State Threshold, V <sub>IL</sub>                         |                   |                                                                 | -                    | 0.8 | -                      | 0.8                  | -                    | 0.8 | -                      | 0.8      | V     |

| High State Threshold, VIH                                    |                   |                                                                 | 2,4                  | -   | 2,4                    | -                    | 2.4                  | -   | 2.4                    | -        | V     |

| Input Current (Low or H<br>I <sub>IL</sub> , I <sub>IH</sub> | ligh),            | V <sub>IN</sub> = 0V or + 15V                                   | -                    | ±1  | -                      | ±1                   | -                    | ±1  | -                      | ±1       | μA    |

| Input Coding                                                 |                   | See Tables 1 & 3                                                | Binary/Offset Binary |     |                        | Binary/Offset Binary |                      |     |                        |          |       |

| Input Capacitance                                            |                   | (Note 3)                                                        | -                    | 4   | -                      | 4                    | -                    | 4   | -                      | 4        | pF    |

| POWER SUPPLY CHA                                             | RACTER            | ISTICS                                                          | -                    | •   | -                      | •                    | -                    | -   | -                      | <u> </u> | -     |

| Power Supply Voltage Range (Note 5)                          |                   | (Note 5)                                                        | +5 to +16            |     |                        | +5 to +16            |                      |     | V                      |          |       |

| l+                                                           |                   | All Digital Inputs High or<br>Low (Excluding Ladder<br>Network) | -                    | 2   | -                      | 2.5                  | -                    | 2   | -                      | 2.5      | mA    |

NOTES:

1. Full scale range (FSR) is 10V for unipolar and  $\pm$ 10V for bipolar modes.

2. Using internal feedback resistor, R<sub>FEEDBACK</sub>.

- 3. Guaranteed by design or characterization and not production tested.

- 4. Accuracy not guaranteed unless outputs at ground potential.

- 5. Accuracy is tested and guaranteed at V+ = +15V, only.

# **Definition of Terms**

**Nonlinearity:** Error contributed by deviation of the DAC transfer function from a "best straight line" through the actual plot of transfer function. Normally expressed as a percentage of full scale range or in (sub)multiples of 1 LSB.

**Resolution:** It is addressing the smallest distinct analog output change that a D/A converter can produce. It is commonly expressed as the number of converter bits. A converter with resolution of n bits can resolve output changes of  $2^{-N}$  of the full-scale range, e.g.  $2^{-N}$  V<sub>REF</sub> for a unipolar conversion. Resolution by no means implies linearity.

**Settling Time:** Time required for the output of a DAC to settle to within specified error band around its final value (e.g. 1/2 LSB) for a given digital input change, i.e. all digital inputs LOW to HIGH and HIGH to LOW.

**Gain Error:** The difference between actual and ideal analog output values at full-scale range, i.e. all digital inputs at HIGH state. It is expressed as a percentage of full-scale range or in (sub)multiples of 1 LSB.

**Feedthrough Error:** Error caused by capacitive coupling from  $V_{REF}$  to  $I_{OUT1}$  with all digital inputs LOW.

**Output Capacitance:** Capacitance from  $I_{OUT1}$ , and  $I_{OUT2}$  terminals to ground.

**Output Leakage Current:** Current which appears on  $I_{OUT1}$ , terminal when all digital inputs are LOW or on  $I_{OUT2}$  terminal when all digital inputs are HIGH.

For further information on the use of this device, see the following Application Notes:

- A002 "Principles of Data Acquisition and Conversion"

- A018 "Do's and Don'ts of Applying A/D Converters", by Peter Bradshaw and Skip Osgood

- A042 "Interpretation of Data Conversion Accuracy Specifications"

# **Detailed Description**

The AD7523 and AD7533 are monolithic multiplying D/A converters. A highly stable thin film R-2R resistor ladder network and NMOS SPDT switches form the basis of the converter circuit, CMOS level shifters permit low power TTL/CMOS compatible operation. An external voltage or current reference and an operational amplifier are all that is required for most voltage output applications.

A simplified equivalent circuit of the DAC is shown in the Functional Diagram. The NMOS SPDT switches steer the ladder leg currents between  $I_{OUT1}$  and  $I_{OUT2}$  buses which must be held at ground potential. This configuration maintains a constant current in each ladder leg independent of the input code.

Converter errors are further reduced by using separate metal interconnections between the major bits and the outputs. Use of high threshold switches reduce offset (leakage) errors to a negligible level.

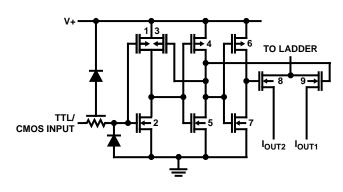

The level shifter circuits are comprised of three inverters with positive feedback from the output of the second to the first, see Figure 1. This configuration results in TTL/CMOS compatible operation over the full military temperature range. With the ladder SPDT switches driven by the level shifter, each switch is binarily weighted for an ON resistance proportional to the respective ladder leg current. This assures a constant voltage drop across each switch, creating equipotential terminations for the 2R ladder resistors and high accurate leg currents.

FIGURE 1. CMOS SWITCH

# **Typical Applications**

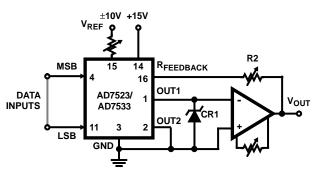

## Unipolar Binary Operation - AD7523 (8 Bit DAC)

The circuit configuration for operating the AD7523 in unipolar mode is shown in Figure 2. With positive and negative  $V_{\mathsf{REF}}$  values the circuit is capable of 2-Quadrant multiplication. The "Digital Input Code/Analog Output Value" table for unipolar mode is given in Table 1.

NOTES:

1. R1 and R2 used only if gain adjustment is required.

2. CF1 protects AD7523 and AD7533 against negative transients.

#### FIGURE 2. UNIPOLAR BINARY OPERATION

| ANALOG OUTPUT                                                  |  |  |  |  |  |

|----------------------------------------------------------------|--|--|--|--|--|

| $-V_{REF}(\frac{255}{256})$                                    |  |  |  |  |  |

| $-V_{REF}(\frac{129}{256})$                                    |  |  |  |  |  |

| $-V_{\text{REF}}(\frac{128}{256}) = -\frac{V_{\text{REF}}}{2}$ |  |  |  |  |  |

| $-V_{REF}(\frac{127}{256})$                                    |  |  |  |  |  |

| $-V_{REF}(\frac{1}{256})$                                      |  |  |  |  |  |

| $-V_{\text{REF}}(\frac{0}{256}) = 0$                           |  |  |  |  |  |

|                                                                |  |  |  |  |  |

TABLE 1. UNIPOLAR BINARY CODE - AD7523

NOTES:

1. 1 LSB =

$$(2^{-8}) (V_{\text{REF}}) = (\frac{1}{256}) (V_{\text{REF}})$$

## Zero Offset Adjustment

- 1. Connect all digital inputs to GND.

- 2. Adjust the offset zero adjust trimpot of the output operational amplifier for 0V  $\pm 1 mV$  (max) at V\_{OUT}

## Gain Adjustment

- 1. Connect all digital inputs to V+.

- 2. Monitor  $V_{OUT}$  for a - $V_{REF}$  (1 1/2<sup>8</sup>) reading.

- 3. To increase  $V_{OUT}$ , connect a series resistor, R2, (0 $\Omega$  to 250 $\Omega$ ) in the I<sub>OUT1</sub> amplifier feedback loop.

- 4. To decrease  $V_{OUT}$  connect a series resistor, R1, (0 $\Omega$  to 250 $\Omega$ ) between the reference voltage and the  $V_{REF}$  terminal.

#### Unipolar Binary Operation - AD7533 (10 Bit DAC)

The circuit configuration for operating the AD7533 in unipolar mode is shown in Figure 2. With positive and negative  $V_{\text{REF}}$  values the circuit is capable of 2-Quadrant multiplication. The "Digital Input Code/Analog Output Value" table for unipolar mode is given in Table 2.

#### TABLE 2. UNIPOLAR BINARY CODE - AD7533

| DIGITAL INPUT<br>MSB LSB | (NOTE 1)<br>Nominal Analog Output                 |

|--------------------------|---------------------------------------------------|

| 111111111                | $-V_{REF}(\frac{1023}{1024})$                     |

| 100000001                | $-V_{REF}(\frac{513}{1024})$                      |

| 100000000                | $-V_{REF}(\frac{512}{1024}) = -\frac{V_{REF}}{2}$ |

| 011111111                | $-V_{REF}(\frac{511}{1024})$                      |

| 000000001                | $-V_{REF}(\frac{1}{1024})$                        |

| 000000000                | $-V_{REF}\left(\frac{0}{1024}\right) = 0$         |

NOTES:

- 1.  $V_{OUT}$  as shown in the Functional Diagram.

- 2. Nominal Full Scale for the circuit of Figure 2 is given by

$$FS = -V_{REF} \left(\frac{1023}{1024}\right)$$

3. Nominal LSB magnitude for the circuit of Figure 2 is given by

$$LSB = V_{REF} \left(\frac{1}{1024}\right)$$

## Zero Offset Adjustment

- 1. Connect all digital inputs to GND.

- 2. Adjust the offset zero adjust trimpot of the output operational amplifier for 0V  $\pm 1 mV$  (max) at V\_{OUT}

## Gain Adjustment

- 1. Connect all digital inputs to V+.

- 2. Monitor V<sub>OUT</sub> for a -V<sub>REF</sub> (1 1/2<sup>10</sup>) reading.

- 3. To increase  $V_{OUT}$ , connect a series resistor, R2, (0 $\Omega$  to 250 $\Omega$ ) in the I<sub>OUT1</sub> amplifier feedback loop.

- 4. To decrease  $V_{OUT}$ , connect a series resistor, R1, (0 $\Omega$  to 250 $\Omega$ ) between the reference voltage and the  $V_{REF}$  terminal.

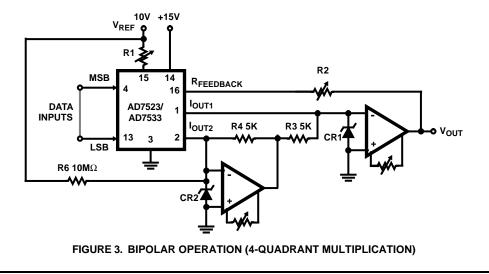

#### **Bipolar (Offset Binary) Operation - AD7523**

The circuit configuration for operating the AD7523 in the bipolar mode is given in Figure 3. Using offset binary digital input codes and positive and negative reference voltage values, Four-Quadrant multiplication can be realized. The "Digital Input Code/Analog Output Value" table for bipolar mode is given in Table 3.)

| •                        |                             |

|--------------------------|-----------------------------|

| DIGITAL INPUT<br>MSB LSB | ANALOG OUTPUT               |

| 1111111                  | $-V_{REF}(\frac{127}{128})$ |

| 10000001                 | $-V_{REF}(\frac{1}{128})$   |

| 1000000                  | 0                           |

| 01111111                 | $+V_{REF}(\frac{1}{128})$   |

| 00000001                 | $+V_{REF}(\frac{127}{128})$ |

| 0000000                  | $+V_{REF}(\frac{128}{128})$ |

#### TABLE 3. BIPOLAR (OFFSET BINARY) CODE - AD7523

NOTES:

1. 1 LSB =

$$(2^{-7}) (V_{\text{REF}}) = (\frac{1}{128}) (V_{\text{REF}})$$

A "Logic 1" input at any digital input forces the corresponding ladder switch to steer the bit current to  $\rm I_{OUT1}$  bus. A "Logic 0" input forces the bit current to  $\rm I_{OUT2}$  bus. For any code the

$I_{OUT1}$  and  $I_{OUT2}$  bus currents are complements of one another. The current amplifier at  $I_{OUT2}$  changes the polarity of  $I_{OUT2}$  current and the transconductance amplifier at  $I_{OUT}$ output sums the two currents. This configuration doubles the output range. The difference current resulting at zero offset binary code, (MSB = "Logic 1", all other bits = "Logic 0"), is corrected by suing an external resistor, (10M $\Omega$ ), from V<sub>REF</sub> to  $I_{OUT2}$  (Figure 3).

### **Offset Adjustment**

- 1. Adjust V<sub>REF</sub> to approximately +10V.

- 2. Connect all digital inputs to "Logic 1".

- 3. Adjust  $I_{OUT2}$  amplifier offset adjust trimpot for 0V  $\pm 1mV$  at  $I_{OUT2}$  amplifier output.

- 4. Connect MSB (Bit 1) to "Logic 1" and all other bits to "Logic 0".

- 5. Adjust  $I_{OUT1}$  amplifier offset adjust trimpot for  $0V\pm 1mV$  at  $V_{OUT}$ .

#### **Gain Adjustment**

- 1. Connect all digital inputs to V+.

- 2. Monitor V<sub>OUT</sub> for a -V<sub>REF</sub> (1 1/2<sup>8</sup>) volts reading.

- 3. To increase  $V_{OUT}$  connect a series resistor, R2, of up to  $250\Omega$  between  $V_{OUT}$  and  $R_{FEEDBACK}.$

- 4. To decrease V<sub>OUT</sub>, connect a series resistor, R1, of up to  $250\Omega$  between the reference voltage and the V<sub>REF</sub> terminal.

#### **Bipolar (Offset Binary) Operation - AD7533**

The circuit configuration for operating the AD7533 in the bipolar mode is given in Figure 3. Using offset binary digital input codes and positive and negative reference voltage values, 4-Quadrant multiplication can be realized. The "Digital Input Code/Analog Output Value" table for bipolar mode is given in Table 4.

A "Logic 1" input at any digital input forces the corresponding ladder switch to steer the bit current to  $I_{OUT1}$  bus. A "Logic 0" input forces the bit current to  $I_{OUT2}$  bus. For any code the  $I_{OUT1}$  and  $I_{OUT2}$  bus currents are complements of one another. The current amplifier at  $I_{OUT2}$  changes the polarity of  $I_{OUT2}$  current and the transconductance amplifier at  $I_{OUT1}$  output sums the two currents. This configuration doubles the output range. The difference current resulting at zero offset binary code, (MSB = "Logic 1", all other bits = "Logic 0"), is corrected by using an external resistor, (10MΩ), from  $V_{REF}$  to  $I_{OUT2}$ .

| TABLE 4: UNIT OLAN BINANT CODE - ADT555 |                                      |  |  |  |  |

|-----------------------------------------|--------------------------------------|--|--|--|--|

| DIGITAL INPUT<br>MSB LSB                | (NOTE 1)<br>NOMINAL ANALOG OUTPUT    |  |  |  |  |

| 111111111                               | $-V_{\text{REF}}(\frac{511}{512})$   |  |  |  |  |

| 100000001                               | $-V_{REF}(\frac{1}{512})$            |  |  |  |  |

| 100000000                               | 0                                    |  |  |  |  |

| 011111111                               | $+V_{REF}\left(\frac{1}{512}\right)$ |  |  |  |  |

| 000000001                               | $+V_{REF}(\frac{511}{512})$          |  |  |  |  |

| 000000000                               | $+V_{\text{REF}}(\frac{512}{512})$   |  |  |  |  |

TABLE 4. UNIPOLAR BINARY CODE - AD7533

NOTES:

- 1.  $V_{OUT}$  as shown in the Functional Diagram.

- 2. Nominal Full Scale for the circuit of Figure 6 is given by

$$FSR = V_{REF} \left( \frac{1023}{512} \right)$$

3. Nominal LSB magnitude for the circuit of Figure 3 is given by 1 + 2B = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1

$$LSB = V_{REF} \left( \frac{1}{512} \right)$$

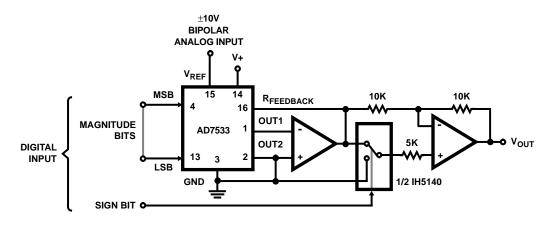

FIGURE 4. 10-BIT AND SIGN MULTIPLYING DAC

#### **Offset Adjustment**

- 1. Adjust V<sub>REF</sub> to approximately +10V.

- 2. Connect all digital inputs to "Logic 1".

- 3. Adjust  $I_{OUT2}$  amplifier offset adjust trimpot for 0V  $\pm 1mV$  at  $I_{OUT2}$  amplifier output.

- 4. Connect MSB (Bit 1) to "Logic 1" and all other bits to "Logic 0".

- 5. Adjust  $I_{OUT1}$  amplifier offset adjust trimpot for 0V  $\pm 1mV$  at  $V_{OUT}$

#### **Gain Adjustment**

- 1. Connect all digital inputs to V+.

- 2. Monitor V<sub>OUT</sub> for a -V<sub>REF</sub> (1 2<sup>-9</sup>) volts reading.

- 3. To increase V<sub>OUT</sub>, connect a series resistor of up to 250 $\Omega$  between V<sub>OUT</sub> and R<sub>FEEDBACK</sub>.

- 4. To decrease  $V_{OUT}$ , connect a series resistor of up to 250 $\Omega$  between the reference voltage and the  $V_{REF}$  terminal.

# **Die Characteristics**

## DIE DIMENSIONS:

101 x 103mils (2565 x 2616micrms)

## **METALLIZATION:**

Type: Pure Aluminum Thickness:  $10 \pm 1k \text{\AA}$

## **GLASSIVATION:**

Type: PSG/Nitride PSG:  $7 \pm 1.4k \text{\AA}$ Nitride:  $8 \pm 1.2k \text{\AA}$

PROCESS: CMOS Metal Gate

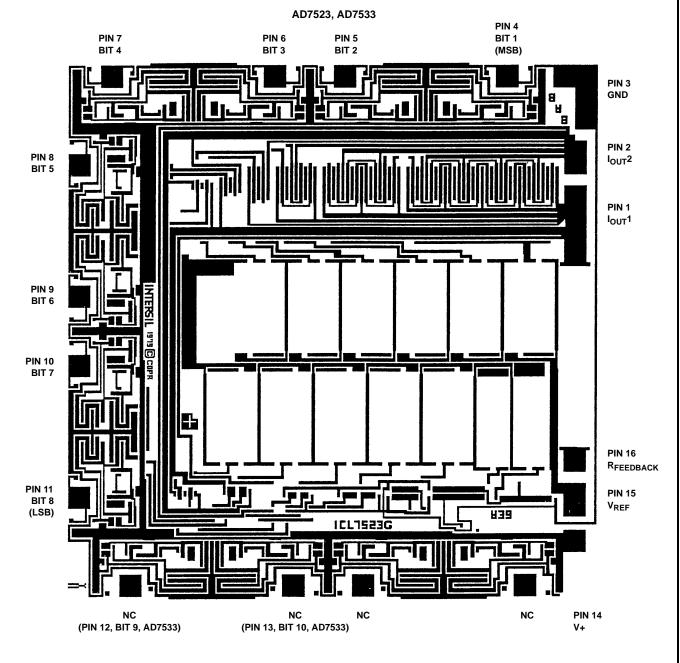

# Metallization Mask Layout