## 1-/2-Channel +15V Digital Potentiometers AD5260/AD5262

#### FEATURES

256 Position AD5260 – 1-Channel AD5262 – 2-Channel (Independently Programmable) Potentiometer Replacement 20K, 50K, 200K Ohm 3-Wire SPI Compatible Serial Data Input +5 to +15V Single-Supply; ±5.5V Dual-Supply Operation Power ON Mid-Scale Preset

#### APPLICATIONS

Mechanical Potentiometer Replacement Instrumentation: Gain, Offset Adjustment Programmable Voltage to Current Conversion Programmable Filters, Delays, Time Constants Line Impedance Matching

#### GENERAL DESCRIPTION

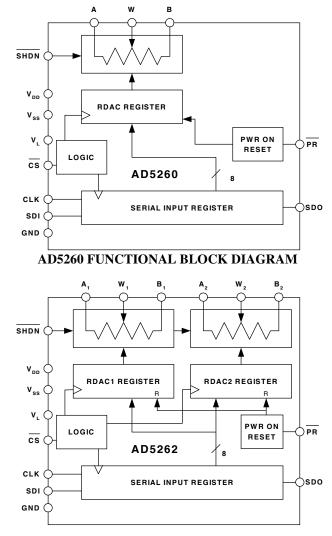

The AD5260/AD5262 provides a single or dual channel, 256 position, digitally-controlled variable resistor (VR) device. These devices perform the same electronic adjustment function as a potentiometer or variable resistor. Each Channel of the AD5260/AD5262 contains a fixed resistor with a wiper contact that taps the fixed resistor value at a point determined by a digital code loaded into the SPI compatible serial-input register. The resistance between the wiper and either end point of the fixed resistor varies linearly with respect to the digital code transferred into the VR latch. The variable resistor offers a completely programmable value of resistance, between the A terminal and the wiper or the B terminal and the wiper. The fixed A to B terminal resistance of 20K, 50K or 200K $\Omega$  has a nominal temperature coefficient of 30 ppm/°C.

Each VR has its own VR latch, which holds its programmed resistance value. These VR latches are updated from an internal serial-to-parallel shift register, which is loaded from a standard 3-wire serial-input digital interface. The AD5260 contains an 8-bit serial register while the AD5262 contains a 9-bit serial register. Each bit is clocked into the register on the positive edge of the CLK. The AD5262 address bit determines the corresponding VR latch to be loaded with the last 8-bits of the data word during the positive edging of  $\overline{CS}$  strobe. A serial data output pin at the opposite end of the serial register enables simple daisy-chaining in multiple VR applications without additional external decoding logic.

An optional reset ( $\overline{PR}$ ) pin forces the wiper to the midscale position by loading  $80_{H}$  into the VR latch.

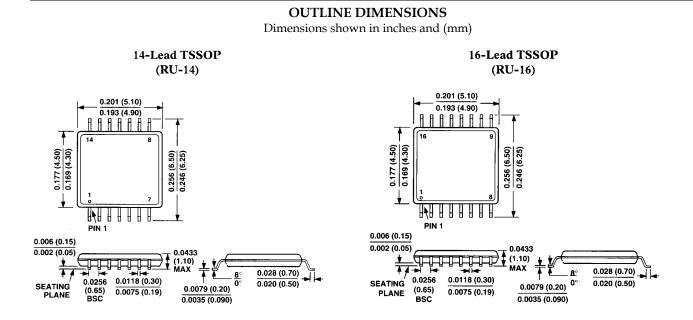

The AD5260/AD5262 are available ultra compact thin surface mount TSSOP-14 and 16. All parts are guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### REV PrC 27 MAR'01

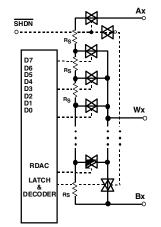

#### AD5262 FUNCTIONAL BLOCK DIAGRAM

#### ORDERING GUIDE

| Model        | Kilo<br>Ohms | Temp      | Package<br>Description | Package<br>Option |

|--------------|--------------|-----------|------------------------|-------------------|

| AD5260BRU20  | 20           | -40/+85°C | TSSOP-14               | RU-14             |

| AD5260BRU50  | 50           | -40/+85°C | TSSOP-14               | RU-14             |

| AD5260BRU200 | 200          | -40/+85°C | TSSOP-14               | RU-14             |

| AD5262BRU20  | 20           | -40/+85°C | TSSOP-16               | RU -16            |

| AD5262BRU50  | 50           | -40/+85°C | TSSOP-16               | RU -16            |

| AD5262BRU200 | 200          | -40/+85°C | TSSOP-16               | RU -16            |

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2001

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## 1-/2-Channel +15V Digital Potentiometers AD5260/AD5262

## ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (V<sub>DD</sub> = +5V, V<sub>SS</sub> = -5V, V<sub>L</sub> = +5V,

| $V_A = +V_{DD}, V_B = 0V, -40^{\circ}C < T_A < +8$<br>Parameter | 5°C unless ot<br>Symbol      | herwise noted.)<br><b>Conditions</b>                                | Min  | Typ <sup>1</sup> | Max             | Units  |

|-----------------------------------------------------------------|------------------------------|---------------------------------------------------------------------|------|------------------|-----------------|--------|

| DC CHARACTERISTICS RHEOSTAT MOD                                 | E Specifications             | apply to all VRs                                                    |      |                  |                 |        |

| Resistor Differential NL <sup>2</sup>                           | R-DNL                        | R <sub>WB</sub> , V <sub>A</sub> =NC                                | -1   | ±1/4             | +1              | LSB    |

| Resistor Nonlinearity <sup>2</sup>                              | R-INL                        | R <sub>WB</sub> , V <sub>A</sub> =NC                                | -2   | ±1/2             | +2              | LSB    |

| Nominal resistor tolerance <sup>3</sup>                         | ΔR                           | $T_A = 25^{\circ}C$                                                 | -30  |                  | 30              | %      |

| Resistance Temperature Coefficient                              | R <sub>AB</sub> / $\Delta$ T | V <sub>AB</sub> = V <sub>DD</sub> , Wiper = No Connect              |      | 50               |                 | ppm/°C |

| Wiper Resistance                                                | R <sub>W</sub>               | I <sub>W</sub> = 1 V/R, V <sub>DD</sub> = +5V                       |      | 50               | 100             | Ω      |

| DC CHARACTERISTICS POTENTIOMETER                                | R DIVIDER MOD                | E Specifications apply to all VRs                                   |      |                  |                 |        |

| Resolution                                                      | N                            |                                                                     | 8    |                  |                 | Bits   |

| Differential Nonlinearity <sup>4</sup>                          | DNL                          |                                                                     | -1   | ±1/4             | +1              | LSB    |

| Integral Nonlinearity <sup>4</sup>                              | INL                          |                                                                     | -2   | ±1/2             | +2              | LSB    |

| Voltage Divider Temperature Coefficient                         | $\Delta V_W / \Delta T$      | Code = 40 <sub>H</sub>                                              |      | 5                |                 | ppm/°C |

| Full-Scale Error                                                | V <sub>WFSE</sub>            | Code = FF <sub>H</sub>                                              | -2   | -1               | +0              | LSB    |

| Zero-Scale Error                                                | V <sub>WZSE</sub>            | Code = 00 <sub>H</sub>                                              | 0    | +1               | +2              | LSB    |

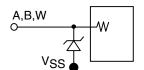

| RESISTOR TERMINALS                                              |                              |                                                                     |      |                  |                 |        |

| Voltage Range <sup>5</sup>                                      | V <sub>A,B,W</sub>           |                                                                     | Vss  |                  | V <sub>DD</sub> | V      |

| Capacitance <sup>6</sup> Ax, Bx                                 | C <sub>A,B</sub>             | $f = 1 MHz$ , measured to GND, Code = $40_H$                        |      | 45               |                 | pF     |

| Capacitance <sup>6</sup> Wx                                     | CW                           | f = 1 MHz, measured to GND, Code = 40 <sub>H</sub>                  |      | 60               |                 | pF     |

| Common-Mode Leakage                                             | Ісм                          | $V_A = V_B = V_{DD} / 2$                                            |      | 1                |                 | nA     |

| DIGITAL INPUTS & OUTPUTS                                        |                              |                                                                     |      |                  |                 |        |

| Input Logic High                                                | V <sub>IH</sub>              |                                                                     | 2.4  |                  |                 | V      |

| Input Logic Low                                                 | V                            |                                                                     |      |                  | 0.8             | V      |

| Input Logic High                                                | V <sub>IH</sub>              | $V_{L} = +3V, V_{SS} = 0V$                                          | 2.1  |                  |                 | V      |

| Input Logic Low                                                 | V                            | $V_{L} = +3V, V_{SS} = 0V$                                          |      |                  | 0.6             | V      |

| Output Logic High                                               | V <sub>OH</sub>              | $R_L = 1K\Omega$ to +5V                                             | 4.9  |                  |                 | V      |

| Output Logic Low                                                | V <sub>OL</sub>              | I <sub>OL</sub> = 1.6mA, V <sub>LOGIC</sub> = +5V                   |      |                  | 0.4             | V      |

| Input Current                                                   | IL                           | $V_{IN} = 0V \text{ or } +5V$                                       |      |                  | ±1              | μA     |

| Input Capacitance <sup>6</sup>                                  | C <sub>IL</sub>              |                                                                     |      | 5                |                 | pF     |

| POWER SUPPLIES                                                  |                              |                                                                     |      |                  |                 |        |

| Logic Supply                                                    | VL                           |                                                                     | 2.7  |                  | 5.5             | V      |

| Power Single-Supply Range                                       | V <sub>DD RANGE</sub>        | V <sub>SS</sub> = 0V                                                | 5    |                  | 16.5            | V      |

| Power Dual-Supply Range                                         | VDD RANGE                    |                                                                     | ±4.5 |                  | ±5.5            | V      |

| Logic Supply Current                                            |                              | V <sub>1</sub> = +5V                                                |      |                  | 60              | μÂ     |

| Positive Supply Current                                         |                              | $V_{IH} = +5V \text{ or } V_{IL} = 0V$                              |      |                  | 1               | μA     |

| Negative Supply Current                                         | I <sub>SS</sub>              | V <sub>SS</sub> = -5V                                               |      |                  | 1               | μA     |

| Power Dissipation <sup>9</sup>                                  | P <sub>DISS</sub>            | $V_{IH} = +5V \text{ or } V_{II} = 0V, V_{DD} = +5V, V_{SS} = -5V$  |      |                  | 0.6             | mW     |

| Power Supply Sensitivity                                        | PSS                          | $\Delta V_{DD} = +5V \pm 10\%$                                      |      | 0.0002           | 0.005           | %/%    |

| DYNAMIC CHARACTERISTICS <sup>6, 10</sup>                        |                              |                                                                     |      |                  |                 |        |

| Bandwidth –3dB                                                  | BW_20K                       | $R_{AB} = 20K\Omega$                                                |      | 400              |                 | KHz    |

| Total Harmonic Distortion                                       | THD <sub>w</sub>             | $V_A = 1$ Vrms, $V_B = 0$ V, f=1KHz, R <sub>AB</sub> = 20K $\Omega$ |      | 0.008            |                 | %      |

| V <sub>w</sub> Settling Time                                    | t <sub>S</sub>               | $V_A$ = 10V, $V_B$ =0V, ±1 LSB error band                           |      | 2                |                 | μs     |

| Resistor Noise Voltage                                          | e <sub>N_WB</sub>            | $R_{WB} = 10K\Omega$ , f = 1KHz, RS = 0                             |      | 9                |                 | nV√Hz  |

REV PrC 27 MAR'01

Information contained in this Preliminary data sheet describes a product in the development stage. There is no guarantee that the information contained here will become a final product in its present form. For latest information contact Walt Heinzer/Analog Devices TEL(408)382-3107; walt heinzer@analog.com

## 1-/2-Channel +15V Digital Potentiometers AD5260/AD5262

ns

ns

ns

ns

ns

### ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (VDD = +5V, VSS = -5V, VL = +5V,

| $V_A = +V_{DD}, V_B = 0V, -40^{\circ}C < T_A < +$ | ,                                |                                 |     |                  |     |       |

|---------------------------------------------------|----------------------------------|---------------------------------|-----|------------------|-----|-------|

| Parameter                                         | Symbol                           | Conditions                      | Min | Typ <sup>1</sup> | Max | Units |

| INTERFACE TIMING CHARACTERIS                      |                                  |                                 |     |                  |     |       |

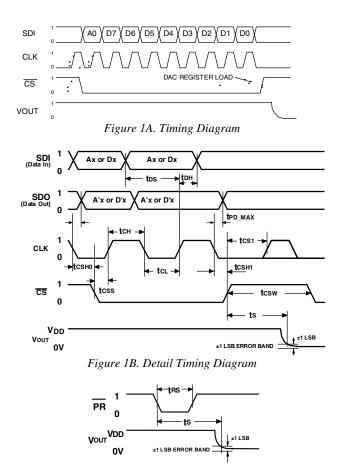

| Input Clock Pulse Width                           | t <sub>CH</sub> ,t <sub>CL</sub> | Clock level high or low         | 50  |                  |     | ns    |

| Data Setup Time                                   | t <sub>DS</sub>                  |                                 | 20  |                  |     | ns    |

| Data Hold Time                                    | t <sub>DH</sub>                  |                                 | 20  |                  |     | ns    |

| CLK to SDO Propagation Delay <sup>13</sup>        | t <sub>PD</sub>                  | $R_L = 1K\Omega$ , $C_L < 20pF$ | 1   |                  | 150 | ns    |

CS Setup Time 20 t<sub>CSS</sub> CS High Pulse Width 40 t<sub>CSW</sub> Reset Pulse Width 90 t<sub>RS</sub> CLK Fall to CS Rise Hold Time 0 t<sub>CSH</sub> CS Rise to Clock Rise Setup 10 t<sub>CS1</sub>

NOTES:

Typicals represent average readings at +25°C and V<sub>DD</sub> = +5V, V<sub>SS</sub> = -5V. 1.

2. Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. Iw = V\_DD/R for both V\_DD=+5V, V\_SS=-5V. 3.

V<sub>AB</sub> = V<sub>DD</sub>, Wiper (V<sub>W</sub>) = No connect INL and DNL are measured at Vw with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0V. 4. DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions.

Resistor terminals A, B, W have no limitations on polarity with respect to each other. 5.

Guaranteed by design and not subject to production test 6

Measured at the Ax terminals. All Ax terminals are open circuited in shutdown mode. 7

Worst case supply current consumed when input all logic-input levels set at 2.4V, standard characteristic of CMOS logic. 8

9. P<sub>DISS</sub> is calculated from (I<sub>DD</sub> x V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

All dynamic characteristics use  $V_{DD}$  = +5V,  $V_{SS}$  = -5V,  $V_L$  = +5V 10

11. Measured at a  $V_W$  pin where an adjacent  $V_W$  pin is making a full-scale voltage change.

See timing diagram for location of measured values. All input control voltages are specified with tp=tp=2ns(10% to 90% of +3V) and timed from a voltage level of 1.5V. Switching characteristics 12. are measured using  $V_L$  = +5V.

13 Propagation delay depends on value of V<sub>DD</sub>, R<sub>L</sub>, and C<sub>L</sub> see applications text.

The AD5260/AD5262 contains 1,968 transistors. Die Size: 89mil x 105mil, 9,345sq. mil. 14.

## 1-/2-Channel +15V Digital Potentiometers

# AD5260/AD5262

#### **ABSOLUTE MAXIMUM RATINGS** ( $T_A = +25^{\circ}C$ , unless

| otherwise noted)                                                        |

|-------------------------------------------------------------------------|

| V <sub>DD</sub> to GND0.3, +15V                                         |

| V <sub>SS</sub> to GND0V, -7V                                           |

| $V_{DD}$ to $V_{SS}$ +15V                                               |

| $V_A, V_B, V_W$ to GND $V_{SS}, V_{DD}$                                 |

| $A_X - B_X, A_X - W_X, B_X - W_X$ ±20mA                                 |

| Digital Inputs & Output Voltage to GND0V, +7V                           |

| Operating Temperature Range40°C to +85°C                                |

| Maximum Junction Temperature (T <sub>J</sub> MAX)+150°C                 |

| Storage Temperature65°C to +150°C                                       |

| Lead Temperature (Soldering, 10 sec)+300°C                              |

| Thermal Resistance <sup>*</sup> $\theta_{JA}$ ,                         |

| TSSOP-14                                                                |

| TSSOP-16                                                                |

| <sup>*</sup> Package Power Dissipation = $(T_JMAX - T_A) / \theta_{JA}$ |

#### **TABLE 1A: AD5260 Serial-Data Word Format**

|                          | DATA      |    |           |           |           |           |           |

|--------------------------|-----------|----|-----------|-----------|-----------|-----------|-----------|

| B7                       | <b>B6</b> | B5 | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> |

| D7                       | D6        | D5 | D4        | D3        | D2        | D1        | D0        |

| $\frac{\text{MSB}}{2^7}$ |           |    |           |           |           |           | LSB       |

| $2^{7}$                  |           |    |           |           |           |           | $2^{0}$   |

#### TABLE 1B: AD5262 Serial-Data Word Format

| ADDR |           | ]         | DATA |           |           |           |           |         |

|------|-----------|-----------|------|-----------|-----------|-----------|-----------|---------|

| B8   | <b>B7</b> | <b>B6</b> | B5   | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | B0      |

| A0   | D7        | D6        | D5   | D4        | D3        | D2        | D1        | D0      |

|      | MSB       |           |      |           |           |           |           | LSB     |

| 28   | 27        |           |      |           |           |           |           | $2^{0}$ |

Figure 1C. AD5260 Preset Timing Diagram

REV PrC 27 MAR'01

## 1-/2-Channel +15V Digital Potentiometers AD5260/AD5262

#### AD5260 PIN CONFIGURATION

| A1                       | 1 | 14 | SDO                      |

|--------------------------|---|----|--------------------------|

| W1                       | 2 | 13 | NC                       |

| B1                       | 3 | 12 | VL                       |

| $\mathbf{V}_{\text{DD}}$ | 4 | 11 | $\mathbf{V}_{\text{ss}}$ |

| SHDN                     | 5 | 10 | GND                      |

| CLK                      | 6 | 9  | PR                       |

| SDI                      | 7 | 8  | CS                       |

|                          |   |    |                          |

#### **TABLE 2:** AD5260 PIN Descriptions

| Pin | Name            | Description                                                |

|-----|-----------------|------------------------------------------------------------|

| 1   | А               | A Terminal                                                 |

| 2   | W               | Wiper, addr=0 <sub>2</sub>                                 |

| 3   | В               | B Terminal                                                 |

| 4   | $V_{DD}$        | Positive power supply, specified for                       |

|     |                 | operation at both +5V or 15V. (Sum of                      |

|     |                 | $ V_{DD}  +  V_{SS}  \le 15V)$                             |

| 5   | SHDN            | Active low input. Terminal A open-                         |

|     |                 | circuit. Shutdown controls Variable                        |

|     |                 | Resistors of RDAC                                          |

| 6   | CLK             | Serial Clock Input, positive edge                          |

|     |                 | triggered                                                  |

| 7   | SDI             | Serial Data Input                                          |

| 8   | CS              | Chip Select Input, Active Low. When                        |

|     |                 | $\overline{\mathrm{CS}}$ returns high, data will be loaded |

|     |                 | into the DAC register.                                     |

| 9   | PR              | Active low preset to mid-scale; sets                       |

|     |                 | RDAC registers to 80 <sub>H</sub>                          |

| 10  | GND             | Ground                                                     |

| 11. | V <sub>SS</sub> | Negative Power Supply, specified for                       |

|     |                 | operation from 0V to -5V                                   |

| 12  | $V_L$           | Logic Supply Voltage, needs to be                          |

|     |                 | same voltage as the digital logic                          |

|     |                 | controlling the AD5260.                                    |

| 13  | NC              | No Connect                                                 |

| 14  | SDO             | Serial Data Output, Open Drain                             |

|     |                 | transistor requires pull-up resistor.                      |

#### AD5262 PIN CONFIGURATION

| SDO                      | 1 | 16 | A2                       |

|--------------------------|---|----|--------------------------|

| A1                       | 2 | 15 | W2                       |

| W1                       | 3 | 14 | B2                       |

| B1                       | 4 | 13 | VL                       |

| $\mathbf{V}_{\text{DD}}$ | 5 | 12 | $\mathbf{V}_{\text{SS}}$ |

| SHDN                     | 6 | 11 | GND                      |

| CLK                      | 7 | 10 | PR                       |

| SDI                      | 8 | 9  | CS                       |

|                          |   | 1  |                          |

#### TABLE 3: AD5262 PIN Descriptions

| Pin | Name            | Description                                                     |

|-----|-----------------|-----------------------------------------------------------------|

| 1   | SDO             | Serial Data Output, Open Drain                                  |

|     |                 | transistor requires pull-up resistor.                           |

| 2   | A1              | A Terminal RDAC #1                                              |

| 3   | W1              | Wiper RDAC #1, address $A0=0_2$                                 |

| 4   | B1              | B Terminal RDAC #1                                              |

| 5   | $V_{DD}$        | Positive power supply, specified for                            |

|     |                 | operation at both +5V or +15V. (Sum                             |

|     |                 | of $ V_{DD}  +  V_{SS}  \le 15V$                                |

| 6   | SHDN            | Active low input. Terminal A open-                              |

|     |                 | circuit. Shutdown controls Variable                             |

|     |                 | Resistors #1 through #2                                         |

| 7   | CLK             | Serial Clock Input, positive edge                               |

|     |                 | triggered                                                       |

| 8   | SDI             | Serial Data Input                                               |

| 9   | CS              | Chip Select Input, Active Low. When                             |

|     |                 | $\overline{\mathrm{CS}}$ returns high, data in the serial input |

|     |                 | register is decoded based on the                                |

|     |                 | address bits and loaded into the target                         |

|     |                 | DAC register.                                                   |

| 10  | PR              | Active low preset to mid-scale; sets                            |

|     |                 | RDAC registers to 80 <sub>H</sub>                               |

| 11  | GND             | Ground                                                          |

| 12  | V <sub>SS</sub> | Negative Power Supply, specified for                            |

|     |                 | operation at both 0V or -5V (Sum of                             |

|     |                 | $ V_{DD}  +  V_{SS}  < 15V$                                     |

| 13  | $V_L$           | Logic Supply Voltage, needs to be                               |

|     |                 | same voltage as the digital logic                               |

|     |                 | controlling the AD5262.                                         |

| 14  | B2              | B Terminal RDAC #2                                              |

| 15  | W2              | Wiper RDAC #2, address $A0=1_2$                                 |

| 16  | A2              | A Terminal RDAC #2                                              |

REV PrC 27 MAR'01

Information contained in this Preliminary data sheet describes a product in the development stage. There is no guarantee that the information contained here will become a final product in its present form. For latest information contact Walt Heinzer/Analog Devices TEL(408)382-3107; walt.heinzer@analog.com

## 1-/2-Channel +15V Digital Potentiometers

#### **OPERATION**

The AD5260/AD5262 provide a single/dual channel, 256position digitally-controlled variable resistor (VR) device. Changing the programmed VR settings is accomplished by clocking in a 9-bit serial data word into the SDI (Serial Data Input) pin. The format of this data word is one address bit A0 represents the first bit B8, then followed by eight data bits B7-B0 with MSB first. Table 1 provides the serial register data word format. See Table 5 for the AD5260/AD5262 address assignments to decode the location of VR latch receiving the serial register data in bits B7 through B0. VR outputs can be changed one at a time in random sequence. The AD5260/AD5262 presets to a mid-scale by asserting the  $\overline{PR}$  pin, simplifying fault condition recovery at power up. Both parts have an internal power ON preset that places the wiper in a midscale preset condition at power ON. Operation of the power on preset function depends only on the logic pin  $(V_L)$ .

The AD5260/AD5262 contains a power shutdown SHDN pin, which places the RDAC in a zero power consumption state where terminals Ax are open circuited, and the wiper W is connected to B resulting in only leakage currents being consumed in the VR structure. In shutdown mode the VR latch settings are maintained, so that, returning to operational mode from power shutdown, the VR settings return to their previous resistance values.

#### DIGITAL INTERFACING

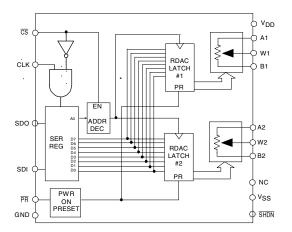

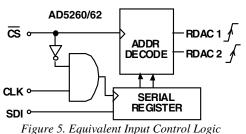

The AD5260/AD5262 contain a standard three-wire serial input control interface. The three inputs are clock (CLK),  $\overline{CS}$  and serial data input (SDI). The positive-edge sensitive CLK input requires clean transitions to avoid clocking incorrect data into the serial input register. Standard logic families work well. If mechanical switches are used for product evaluation they should be debounced by a flip-flop or other suitable means. Figure 3 block diagram shows more detail of the internal digital circuitry. When  $\overline{CS}$  is low, the clock loads data into the serial register on each positive clock edge, see Table 4.

Figure 3. Block Diagram

#### **TABLE 4: Input Logic Control Truth Table**

| CLK | CS | $\overline{PR}$ | SHDN | Register Activity                                                                                         |

|-----|----|-----------------|------|-----------------------------------------------------------------------------------------------------------|

| -   |    |                 |      |                                                                                                           |

| L   | L  | Н               | Н    | No SR effect, enables SDO pin                                                                             |

| Р   | L  | Н               | Н    | Shift One bit in from the SDI pin. The<br>eighth previously entered bit is shifted<br>out of the SDO pin. |

| Х   | Р  | Н               | Н    | Load SR data into RDAC latch based on A0 decode (Table 5).                                                |

| Х   | Н  | Н               | Н    | No Operation                                                                                              |

| Х   | Х  | L               | Н    | Sets all RDAC latches to midscale, wiper centered, & SDO latch cleared.                                   |

| Х   | Н  | Р               | Н    | Latches all RDAC latches to 80 <sub>H</sub> .                                                             |

| Х   | Η  | Н               | L    | Open circuits all resistor A-terminals, connects W to B, turns off SDO output transistor.                 |

AD5260/AD5262

NOTE: P = positive edge, X = don't care, SR = shift register

The serial-data-output (SDO) pin contains an open drain nchannel FET. This output requires a pull-up resistor in order to transfer data to the next package's SDI pin. The pull-up resistor termination voltage may be larger than the V<sub>DD</sub> supply of the AD5260/AD5262 SDO output device, e.g., the AD5260/AD5262 could operate at  $V_{DD}$  = 3.3V and the pull-up for interface to the next device could be set at +5V. This allows for daisy chaining several RDACs from a single processor serial-data line. Clock period needs to be increased when using a pull-up resistor to the SDI pin of the following device in series. Capacitive loading at the daisy chain node SDO-SDI between devices may induce time delay to subsequent devices. User should be aware of this potential problem in order to achieve data transfer successfully. When daisy chaining is used, the  $\overline{CS}$ should be kept low until all the bits of every package are clocked into their respective serial registers insuring that the address bit and data bits are in the proper decoding location, see Figure 4. This would require 18 bits of address and data complying to the word format provided in Table 1 if two AD5262 RDACs are daisy chained. During shutdown (SHDN) the SDO output pin is forced to the off (logic high state) to disable power dissipation in the pull up resistor. See figure 6 for equivalent SDO output circuit schematic.

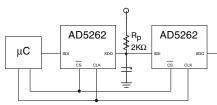

Figure 4. Daisy Chain Configuration

## **TABLE 5.** Address Decode TableA0Latch Loaded

| RDAC#1 | AD5262 |               |

|--------|--------|---------------|

| RDAC#2 | AD5262 |               |

| RDAC#1 | AD5260 |               |

|        |        | RDAC#2 AD5262 |

REV PrC 27 MAR'01

Information contained in this Preliminary data sheet describes a product in the development stage. There is no guarantee that the information contained here will become a final product in its present form. For latest information contact Walt Heinzer/Analog Devices TEL(408)382-3107; walt.heinzer@analog.com

## 1-/2-Channel +15V Digital Potentiometers

The data setup and data hold times in the specification table determine the data valid time requirements. The AD5260 uses an 8-bit serial input data register word that is transferred to the internal RDAC register when the CS line returns to logic high. For AD5262 the last 9 bits of the data word entered into the serial register are held when  $\overline{CS}$  returns high. Any extra bits are ignored. At the same time  $\overline{CS}$  goes high it gates the address decoder enabling AD5262 one of two positive edge triggered AD5262 RDAC latches, see figure 5 detail.

The target RDAC latch is loaded with the last eight bits of the serial data word completing one DAC update. For AD5262, two separate 9 bit data words must be clocked in to change both VR settings.

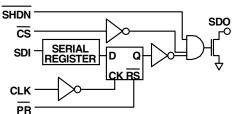

Figure 6. Detail SDO output schematic of the AD5260

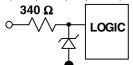

All digital inputs are protected with a series input resistor and parallel Zener ESD structure shown in figure 8. Applies to digital input pins  $\overline{CS}$ , SDI, SDO,  $\overline{PR}$ ,  $\overline{SHDN}$ , CLK

Figure 7. ESD Protection of digital pins

Figure 8. ESD Protection of Resistor Terminals

AD5260/AD5262

Figure 9. AD5260/AD5262 Equivalent RDAC Circuit

#### PROGRAMMING THE VARIABLE RESISTOR Rheostat Operation

The nominal resistances of the RDAC between terminals A and B are available with values of  $20K\Omega$ ,  $50K\Omega$ , and  $200K\Omega$ . The final three digits of the part number determine the nominal resistance value, e.g.  $20K\Omega = 20$ ;  $50K\Omega = 50$ ;  $200K\Omega = 200$ . The nominal resistance (RAB) of the VR has 256 contact points accessed by the wiper terminal, plus the B terminal contact. The eight bit data in the RDAC latch is decoded to select one of the 256 possible settings. Assume a  $20K\Omega$  part is used, the wiper's first connection starts at the B terminal for data 00<sub>H</sub>. Since there is a  $60\Omega$  wiper contact resistance, such connection yields a minimum of  $60\Omega$  resistance between terminals W and B. The second connection is the first tap point corresponds to  $138\Omega$  $(R_{WB} = R_{AB}/256 + R_W = 78\Omega+60\Omega)$  for data  $01_H$ . The third connection is the next tap point representing  $216\Omega$  (78x2+60) for data 02<sub>H</sub> and so on. Each LSB data value increase moves the wiper up the resistor ladder until the last tap point is reached at 19982 $\Omega$  [R<sub>AB</sub>-1LSB+R<sub>w</sub>]. The wiper does not directly connect to the B terminal. See Figure 9 for a simplified diagram of the equivalent RDAC circuit.

The general equation determining the digitally programmed output resistance between W and B is:

$$R_{WB}(D) = \frac{D}{256} \cdot R_{AB} + R_W \qquad \text{eqn.1}$$

where D is the decimal equivalent of the binary code which is loaded in the 8-bit RDAC register, and  $R_{AB}$  is the nominal end-to-end resistance.

For example,  $R_{AB}=20K\Omega$ , when  $V_B = 0V$  and A-terminal is open circuit, the following output resistance values  $R_{WB}$  will be set for the following RDAC latch codes. Result will be the same if terminal A is tied to W:

REV PrC 27 MAR'01

Information contained in this Preliminary data sheet describes a product in the development stage. There is no guarantee that the information contained here will become a final product in its present form. For latest information contact Walt Heinzer/Analog Devices TEL(408)382-3107; walt.heinzer@analog.com

## 1-/2-Channel +15V Digital Potentiometers

# Output State of voltage is equ divided by the 2: the AD5260/AD Full-Scale (R<sub>AB</sub> - 1LSB + R<sub>w</sub>) equation defining Mid-Scale ground for any g

256199826ΩFull-Scale ( $R_{AB}$  - 1LSB +  $R_w$ )12810060ΩMid-Scale1138Ω1 LSB060ΩZero-Scale (Wiper contact resistance)

D

(DEC)

R<sub>WB</sub>

(Ohmş)

In the zero-scale condition a finite wiper resistance of  $60\Omega$  is present. Care should be taken to limit the current flow between W and B in this state to a maximum current of no more than 5mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the RDAC between the wiper W and terminal A also produces a digitally controlled resistance  $R_{WA}$ . When these terminals are used the B-terminal should be let open or tied to the wiper terminal. Setting the resistance value for  $R_{WA}$  starts at a maximum value of resistance and decreases as the data loaded in the latch is increased in value. The general equation for this operation is:

$$R_{WA}(D) = \frac{256 - D}{256} \cdot R_{AB} + R_W \qquad \text{eqn}$$

For example,  $R_{AB}=20K\Omega$ , when  $V_A = 0V$  and B-terminal is open, the following output resistance  $R_{WA}$  will be set for the following RDAC latch codes. Result will be the same if terminal B is tied to W:

2

| R <sub>WA</sub> | Output State                                                 |

|-----------------|--------------------------------------------------------------|

| $(\Omega)$      |                                                              |

|                 |                                                              |

| 60              | Full-Scale                                                   |

| 10060           | Mid-Scale                                                    |

| 19982           | 1 LSB                                                        |

| 20060           | Zero-Scale                                                   |

|                 | <ul><li>(Ω)</li><li>60</li><li>10060</li><li>19982</li></ul> |

The typical distribution of the nominal resistance  $R_{AB}$  from channel-to-channel matches within ±1%. Device to device matching is process lot dependent and is possible to have ±30% variation. Since the resistance element is processed in thin film technology, the change in  $R_{AB}$  with temperature has a 30 ppm/°C temperature coefficient.

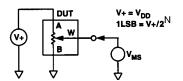

#### **PROGRAMMING THE POTENTIOMETER DIVIDER** Voltage Output Operation

The digital potentiometer easily generates output voltages at wiper-to-B and wiper-to-A to be proportional to the input voltage at A-to-B. Let's ignore the effect of the wiper resistance at the moment. For example connecting A-terminal to +5V and B-terminal to ground produces an output voltage at the wiper-to-B starting at zero volts up to 1 LSB less than +5V. Each LSB

of voltage is equal to the voltage applied across terminal AB divided by the 256 position of the potentiometer divider. Since the AD5260/AD5262 operates from dual supplies, the general equation defining the output voltage at  $V_w$  with respect to ground for any given input voltage applied to terminals AB is:

AD5260/AD5262

$$V_W(D) = \frac{D}{256} V_A + \frac{256 - D}{256} V_B \qquad \text{eqn. 3}$$

where D is decimal equivalent of the binary code, which is loaded in the 8-bit RDAC register.

Operation of the digital potentiometer in the divider mode results in more accurate operation over temperature. Unlike the rheostat mode, the output voltage is dependent on the ratio of the internal resistors  $R_{WA}$  and  $R_{WB}$  and not the absolute values, therefore, the drift reduces to 5ppm/°C.

REV PrC 27 MAR'01

## 1-/2-Channel +15V Digital Potentiometers

## AD5260/AD5262

#### TEST CIRCUITS

Figures 10 to 18 define the test conditions used in product specification table.

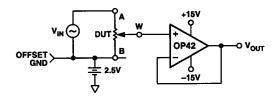

Figure 10. Potentiometer Divider Nonlinearity error test circuit (INL, DNL)

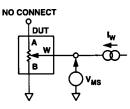

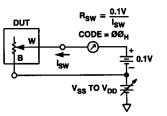

Figure 11. Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

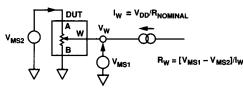

Figure 12. Wiper Resistance test Circuit

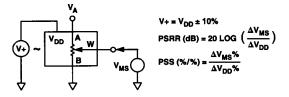

Figure 13. Power supply sensitivity test circuit (PSS, PSSR)

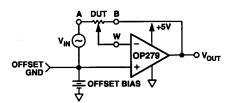

Figure 14. Inverting Gain test Circuit

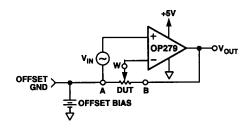

Figure 15. Non-Inverting Gain test circuit

Figure 16. Gain Vs Frequency test circuit

Figure 17. Incremental ON Resistance Test Circuit

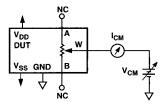

Figure 18. Common Mode Leakage current test circuit

REV PrC 27 MAR'01

## 1-/2-Channel +15V Digital Potentiometers

AD5260/AD5262