SLAS361 - DECEMBER 2001

- Low Supply Voltage Range 1.8 V 3.6 V

- Ultralow-Power Consumption:

- Active Mode: 200 μA at 1 MHz, 2.2 V

Standby Mode: 0.7 μA

- Off Mode (RAM Retention): 0.1 μA

- Five Power Saving Modes

- Wake-Up From Standby Mode in 6 μs

- 16-Bit RISC Architecture, 125 ns Instruction Cycle Time

- Basic Clock Module Configurations:

- Various Internal Resistors

- Single External Resistor

- 32-kHz Crystal

- High Frequency Crystal

- Resonator

- External Clock Source

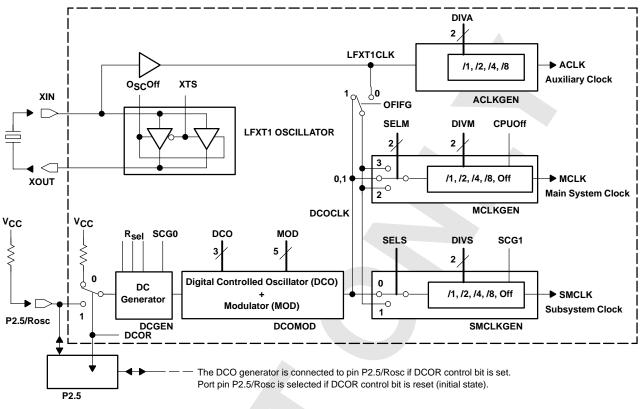

- 16-Bit Timer With Three Capture/Compare Registers

- 10-Bit, 200-ksps A/D Converter With Internal Reference, Sample-and-Hold, Autoscan, and Data Transfer Controller

- Serial Communication Interface (USART) With Software-Selectable Asynchronous UART or Synchronous SPI (MSP430x12x2 Only)

- Serial Onboard Programming

- Programmable Code Protection by Security Fuse

- Supply Voltage Brownout Protection

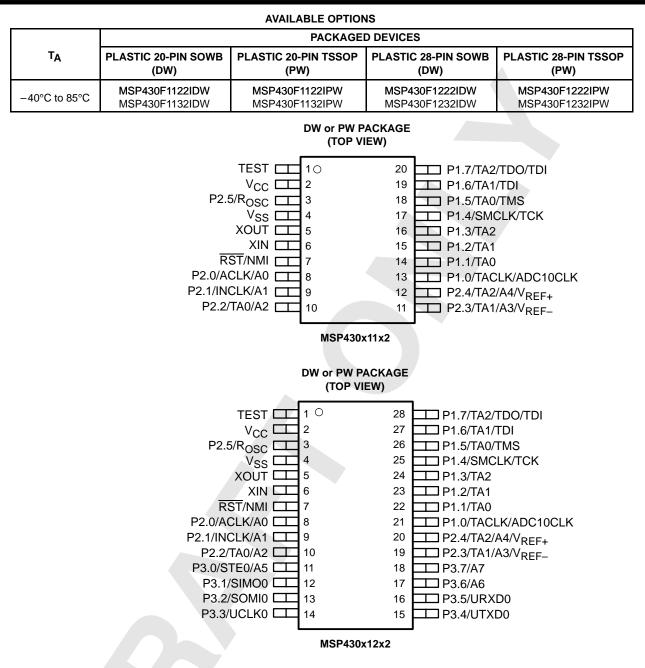

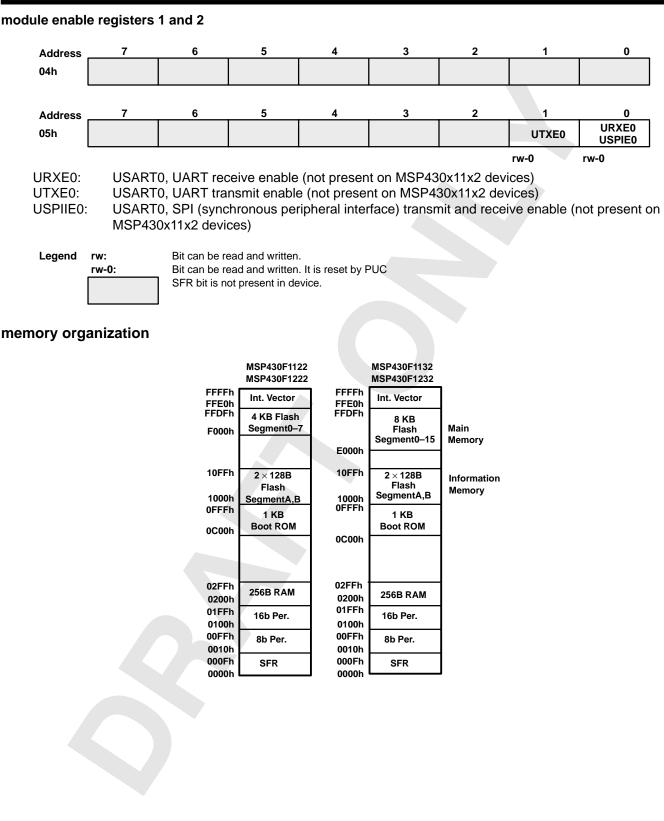

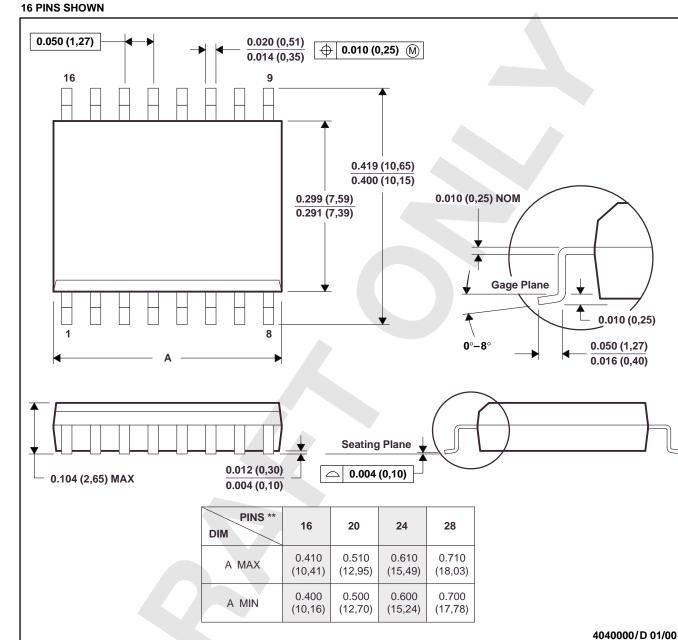

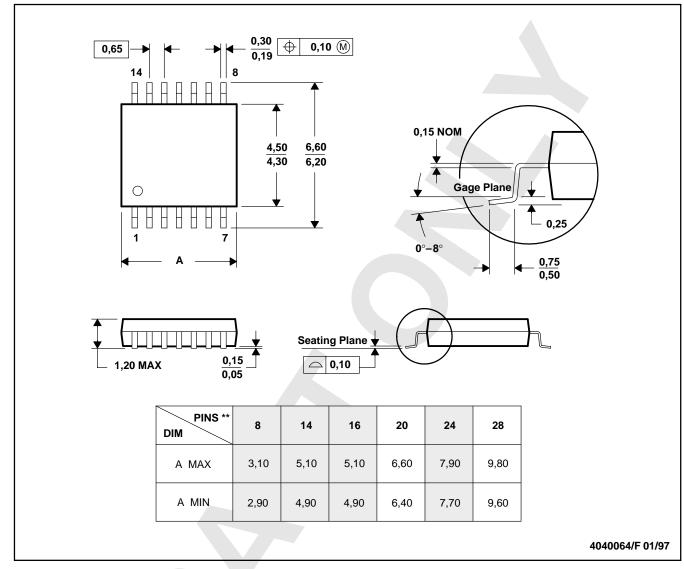

- MSP430x11x2 Family Members Include: MSP430F1122: 4KB + 256B Flash Memory (MTP†), 256B RAM

MSP430F1132: 8KB + 256B Flash Memory (MTP†), 256B RAM

Available in 20-Pin Plastic SOWB and 20-Pin Plastic TSSOP Packages

- MSP430x12x2 Family Members Include: MSP430F1222: 4KB + 256B Flash Memory (MTP†), 256B RAM

MSP430F1232: 8KB + 256B Flash Memory (MTP†), 256B RAM

Available in 28-Pin Plastic SOWB and 28-Pin Plastic TSSOP Packages

- For Complete Module Descriptions, See the MSP430x1xx Family User's Guide, Literature Number SLAU049

## description

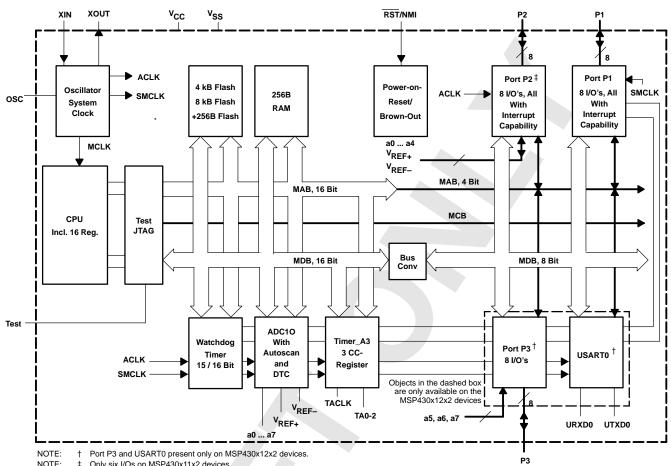

The Texas Instruments MSP430 series is an ultralow-power microcontroller family consisting of several devices featuring different sets of modules targeted to various applications. The microcontroller is designed to be battery operated for an extended-application lifetime. With 16-bit RISC architecture, 16-bit integrated registers on the CPU, and a constant generator, the MSP430 achieves maximum code efficiency. The digitally-controlled oscillator provides fast wake-up from all low-power modes to active mode in less than 6 µs.

The 10-bit A/D converter, together with its integrated reference voltage, provides up to 200 kilosamples-per-second. The peripheral data transfer controller minimizes interrupt overhead and frees up CPU resources. Digital signal processing with the 16-bit RISC performance enables effective system solutions such as glass breakage detection with signal analysis (including wave digital filter algorithm). Another area of application is in stand-alone RF sensors. The MSP430x11x2 and MSP430x12x2 series are ultralow-power mixed signal microcontrollers with a built-in 16-bit timer and fourteen or twenty-two I/O pins.

The flash memory provides added flexibility of in-system programming and data storage without significantly increasing the current consumption of the device. The programming voltage is generated on-chip, thereby alleviating the need for an additional supply, and even allowing for reprogramming of battery-operated systems.

The MSP430x12x2 series microcontrollers have built-in communication capability using asynchronous (UART) and synchronous (SPI) protocols.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup>MTP = Multiple Time Programmable

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

Copyright © 2001, Texas Instruments Incorporated

SLAS361 - DECEMBER 2001

SLAS361 - DECEMBER 2001

NOTE: ‡ Only six I/Os on MSP430x11x2 devices.

functional block diagram

**PRODUCT PREVIEW**

SLAS361 - DECEMBER 2001

## **Terminal Functions**

| TERMIN                        | AL           |              |     |                                                                                                                                                |

|-------------------------------|--------------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                          | '11x2<br>NO. | '12x2<br>NO. | I/O | DESCRIPTION                                                                                                                                    |

| P1.0/TACLK/<br>ADC10CLK       | 13           | 21           | I/O | General-purpose digital I/O pin/Timer_A, clock signal TACLK input/conversion clock—10-bit ADC                                                  |

| P1.1/TA0                      | 14           | 22           | I/O | General-purpose digital I/O pin/Timer_A, capture: CCI0A input, compare: Out0 output                                                            |

| P1.2/TA1                      | 15           | 23           | I/O | General-purpose digital I/O pin/Timer_A, capture: CCI1A input, compare: Out1 output                                                            |

| P1.3/TA2                      | 16           | 24           | I/O | General-purpose digital I/O pin/Timer_A, capture: CCI2A input, compare: Out2 output                                                            |

| P1.4/SMCLK/TCK                | 17           | 25           | I/O | General-purpose digital I/O pin/SMCLK signal output/test clock, input terminal for device programming and test                                 |

| P1.5/TA0/TMS                  | 18           | 26           | I/O | General-purpose digital I/O pin/Timer_A, compare: Out0 output/test mode select, input terminal for device programming and test                 |

| P1.6/TA1/TDI                  | 19           | 27           | I/O | General-purpose digital I/O pin/Timer_A, compare: Out1 output/test data input terminal                                                         |

| P1.7/TA2/TDO/TDI <sup>†</sup> | 20           | 28           | I/O | General-purpose digital I/O pin/Timer_A, compare: Out2 output/test data output terminal or data input during programming                       |

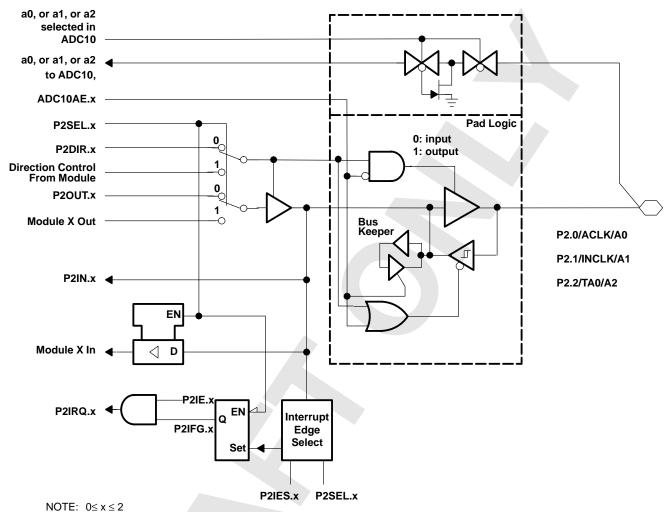

| P2.0/ACLK/A0                  | 8            | 8            | I/O | General-purpose digital I/O pin/ACLK output, analog input to 10-bit ADC input A0                                                               |

| P2.1/INCLK/A1                 | 9            | 9            | I/O | General-purpose digital I/O pin/Timer_A, clock signal at INCLK, analog input to 10-bit ADC input A1                                            |

| P2.2/TA0/A2                   | 10           | 10           | I/O | General-purpose digital I/O pin/Timer_A, capture: CCI0B input/analog input to 10-bit ADC input A2                                              |

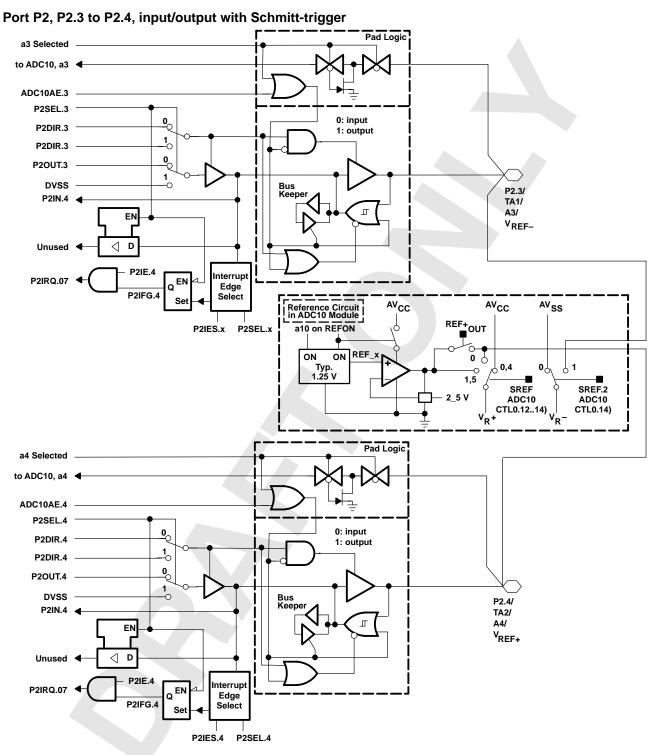

| P2.3/TA1/A3/VREF-             | 11           | 19           | I/O | General-purpose digital I/O pin/Timer_A, compare: Out1 output/analog input to 10-bit ADC input A3, negative reference voltage terminal.        |

| P2.4/TA2/A4/VREF+             | 12           | 20           | I/O | General-purpose digital I/O pin/Timer_A, compare: Out2 output/analog input to 10-bit ADC input A4, I/O of positive reference voltage terminal. |

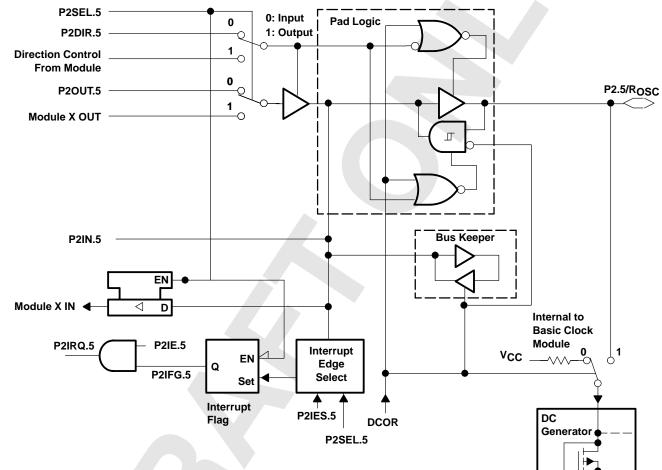

| P2.5/R <sub>OSC</sub>         | 3            | 3            | I/O | General-purpose digital I/O pin/Input for external resistor that defines the DCO nominal frequency                                             |

| P3.0/STE0/A5                  | NA           | 11           | I/O | General-purpose digital I/O pin, slave transmit enable—USART0/SPI mode, analog input to 10-bit ADC input A5                                    |

| P3.1/SIMO0                    | NA           | 12           | I/O | General-purpose digital I/O pin, slave in/master out of USART0/SPI mode                                                                        |

| P3.2/SOMI0                    | NA           | 13           | I/O | General-purpose digital I/O pin, slave out/master in of USART0/SPI mode                                                                        |

| P3.3/UCLK0                    | NA           | 14           | I/O | General-purpose digital I/O pin, external clock input—USART0/UART or SPI mode,<br>clock output—USART0/SPI mode clock input                     |

| P3.4/UTXD0                    | NA           | 15           | I/O | General-purpose digital I/O pin, transmit data out—USART0/UART mode                                                                            |

| P3.5/URXD0                    | NA           | 16           | I/O | General-purpose digital I/O pin, receive data in—USART0/UART mode                                                                              |

| P3.6/A6                       | NA           | 17           | I/O | General-purpose digital I/O pin, analog input to 10-bit ADC input A6                                                                           |

| P3.7/A7                       | NA           | 18           | I/O | General-purpose digital I/O pin, analog input to 10-bit ADC input A7                                                                           |

| RST/NMI                       | 7            | 7            |     | Reset or nonmaskable interrupt input                                                                                                           |

| TEST                          | 1            | 1            |     | Select of test mode for JTAG pins on Port1                                                                                                     |

| V <sub>CC</sub>               | 2            | 2            |     | Supply voltage                                                                                                                                 |

| V <sub>SS</sub>               | 4            | 4            |     | Ground reference                                                                                                                               |

| XIN                           | 6            | 6            | 1   | Input terminal of crystal oscillator                                                                                                           |

| XOUT                          | 5            | 5            | I/O | Output terminal of crystal oscillator                                                                                                          |

<sup>†</sup> TDO or TDI is selected via JTAG instruction.

SLAS361 - DECEMBER 2001

#### short-form description

#### processing unit

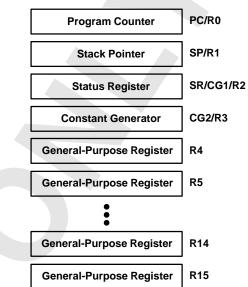

The processing unit is based on a consistent and orthogonally-designed CPU and instruction set. This design structure results in a RISC-like architecture, highly transparent to the application development, and noted for its programming simplicity. All operations other than program-flow instructions are consequently performed as register operations in conjunction with seven addressing modes for source and four modes for destination operands.

#### CPU

All 16 registers are located inside the CPU, providing reduced instruction execution time. This reduces a register-register operation execution time to one cycle of the processor.

Four registers are reserved for special use as a program counter, a stack pointer, a status register, and a constant generator. The remaining twelve registers are available as general-purpose registers.

Peripherals are connected to the CPU using a data address and control buses. They can be easily handled with all instructions for memory manipulation.

#### instruction set

The instruction set for this register-register architecture provides a powerful and easy-to-use assembly language. The instruction set consists of 51 instructions with three formats and seven addressing modes. Table 1 provides a summation and example of the three types of instruction formats; the addressing modes are listed in Table 2.

#### **Table 1. Instruction Word Formats**

| Dual operands, source-destination | e.g. ADD R4, R5 | $R4 + R5 \rightarrow R5$   |

|-----------------------------------|-----------------|----------------------------|

| Single operands, destination only | e.g. CALL R8    | $PC \to (TOS),  R8 \to PC$ |

| Relative jump, un-/conditional    | e.g. JNE        | Jump-on equal bit = 0      |

Most instructions can operate on both word and byte data. Byte operations are identified by the suffix B.

Examples:

Instructions for word operationMOVEDE,TONIADD#235h,&MEMPUSHR5SWPBR5

Instructions for byte operation MOV.B EDE,TONI ADD.B #35h,&MEM PUSH.B R5

SLAS361 - DECEMBER 2001

## instruction set (continued)

| ADDRESS MODE           | s            | d            | SYNTAX           | EXAMPLE           | OPERATION                                         |

|------------------------|--------------|--------------|------------------|-------------------|---------------------------------------------------|

| Register               | $\checkmark$ | $\checkmark$ | MOV Rs, Rd       | MOV R10, R11      | $R10 \rightarrow R11$                             |

| Indexed                | $\checkmark$ |              | MOV X(Rn), Y(Rm) | MOV 2(R5), 6(R6)  | $M(2 + R5) \rightarrow M(6 + R6)$                 |

| Symbolic (PC relative) | $\checkmark$ |              | MOV EDE, TONI    |                   | $M(EDE) \rightarrow M(TONI)$                      |

| Absolute               | $\checkmark$ |              | MOV &MEM, &TCDAT |                   | $M(MEM) \rightarrow M(TCDAT)$                     |

| Indirect               | $\checkmark$ |              | MOV @Rn, Y(Rm)   | MOV @R10, Tab(R6) | $M(R10) \rightarrow M(Tab + R6)$                  |

| Indirect autoincrement | $\checkmark$ |              | MOV @Rn+, RM     | MOV @R10+, R11    | $M(R10) \rightarrow R11, R10 + 2 \rightarrow R10$ |

| Immediate              | $\checkmark$ |              | MOV #X, TONI     | MOV #45, TONI     | #45 $\rightarrow$ M(TONI)                         |

#### Table 2. Address Mode Descriptions

NOTE: s = source d = destination Rs/Rd = source register/destination register Rn = register number

Computed branches (BR) and subroutine call (CALL) instructions use the same addressing modes as the other instructions. These addressing modes provide *indirect* addressing, ideally suited for computed branches and calls. The full use of this programming capability permits a program structure different from conventional 8- and 16-bit controllers. For example, numerous routines can easily be designed to deal with pointers and stacks instead of using flag type programs for flow control.

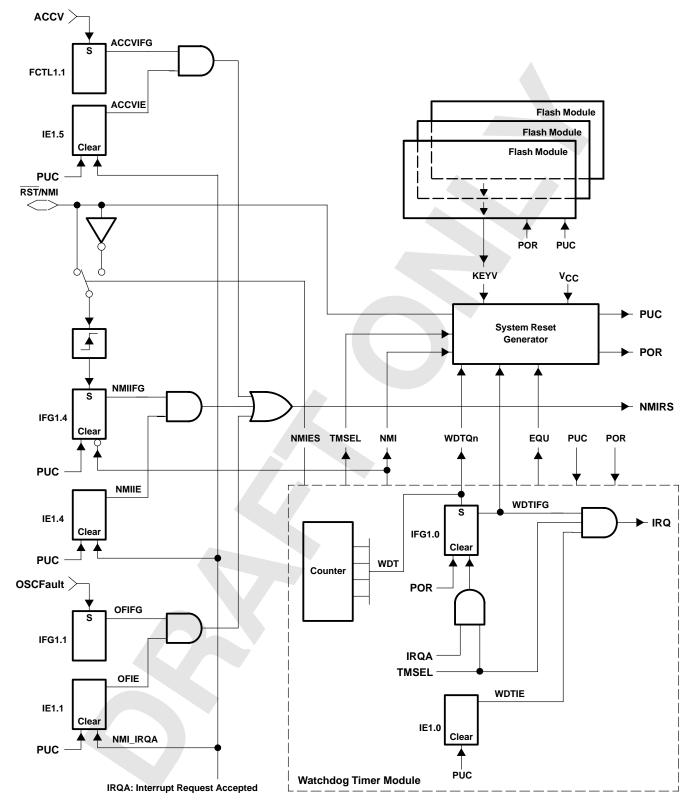

## operation modes and interrupts

The MSP430 operating modes support various advanced requirements for ultralow-power and ultralow-energy consumption. This is achieved by the intelligent management of the operations during the different module operation modes and CPU states. The advanced requirements are fully supported during interrupt event handling. An interrupt event awakens the system from each of the various operating modes and returns with the *RETI* instruction to the mode that was selected before the interrupt event. The different requirements of the CPU and modules, which are driven by system cost and current consumption objectives, necessitate the use of different clock signals:

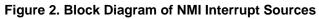

- Auxiliary clock ACLK (from LFXT1CLK/crystal's frequency), used by the peripheral modules

- Main system clock MCLK, used by the CPU and system

- Subsystem clock SMCLK, used by the peripheral modules

## low-power consumption capabilities

The various operating modes are controlled by the software through controlling the operation of the internal clock system. This clock system provides many combinations of hardware and software capabilities to run the application with the lowest power consumption and with optimized system costs:

- Use the internal clock (DCO) generator without any external components.

- Select an external crystal or ceramic resonator for lowest frequency or cost.

- Select and activate the proper clock signals (LFXT1CLK and/or DCOCLK) and clock predivider function.

- Apply an external clock source.

Four of the control bits that influence the operation of the clock system and support fast turnon from low power operating modes are located in the status register SR. The four bits that control the CPU and the system clock generator are SCG1, SCG0, OscOff, and CPUOff.

SLAS361 - DECEMBER 2001

#### status register R2

| _159                                | 8    | 7    | 6    | 5      | 4      | 3    | 2    | 1    | 0    |

|-------------------------------------|------|------|------|--------|--------|------|------|------|------|

| Reserved For Future<br>Enhancements | v    | SCG1 | SCG0 | OscOff | CPUOff | GIE  | N    | z    | с    |

| rw-0                                | rw-0 | rw-0 | rw-0 | rw-0   | rw-0   | rw-0 | rw-0 | rw-0 | rw-0 |

The bits CPUOff, SCG1, SCG0, and OscOff are the most important low-power control bits when the basic function of the system clock generator is established. They are pushed onto the stack whenever an interrupt is accepted and thereby saved so that the previous mode of operation can be retrieved after the interrupt request. During execution of an interrupt handler routine, the bits can be manipulated via indirect access of the data on the stack. This allows the program to resume execution in another power operating mode after the return from interrupt (RETI).

- SCG1: The clock signal SMCLK, used for peripherals, is enabled when bit SCG1 is reset or disabled if the bit is set.

- SCG0: The dc-generator is active when SCG0 is reset. The dc-generator can be deactivated only if the SCG0 bit is set and the DCOCLK signal is not used for MCLK or SMCLK. The current consumed by the dc-generator defines the basic frequency of the DCOCLK. It is a dc current.

The clock signal DCOCLK is deactivated if it is not used for MCLK. There are two situations when the SCG0 bit cannot switch off the dc-generator signal:

- 1. DCOCLK frequency is used for MCLK (CPUOff=0 and SELM.1=0).

- 2. DCOCLK frequency is used for SMCLK (SCG1=0 and SELS=0).

#### NOTE:

When the current is switched off (SCG0=1) the start of the DCOCLK is delayed slightly. The delay is in the  $\mu$ s-range (see device parameters for details).

- OscOff: The LFXT1 crystal oscillator is active when the OscOff bit is reset. The LFXT1 oscillator can only be deactivated if the OscOff bit is set and it is not used for MCLK or SMCLK. The setup time to start a crystal oscillation needs consideration when oscillator off option is used. Mask programmable (ROM) devices can disable this feature so that the oscillator can never be switched off by software.

- CPUOff: The clock signal MCLK, used for the CPU, is active when the CPUOff bit is reset or stopped if it is set.

#### SLAS361 - DECEMBER 2001

#### interrupt vector addresses

The interrupt vectors and the power-up starting address are located in the memory with an address range of 0FFFFh-0FFE0h. The vector contains the 16-bit address of the appropriate interrupt handler instruction sequence.

| INTERRUPT SOURCE                                        | INTERRUPT FLAG                                                                         | SYSTEM INTERRUPT                                     | WORD ADDRESS | PRIORITY    |

|---------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|--------------|-------------|

| Power-up, external reset, watchdog                      | WDTIFG (see Note1)<br>KEYV (see Note 1)                                                | Reset                                                | 0FFFEh       | 15, highest |

| NMI, oscillator fault, flash memory<br>access violation | NMIIFG (see Notes 1 and 4)<br>OFIFG (see Notes 1 and 4)<br>ACCVIFG (see Notes 1 and 4) | (Non)-maskable,<br>(Non)-maskable,<br>(Non)-maskable | 0FFFCh       | 14          |

|                                                         |                                                                                        |                                                      | 0FFFAh       | 13          |

|                                                         |                                                                                        |                                                      | 0FFF8h       | 12          |

|                                                         |                                                                                        |                                                      | 0FFF6h       | 11          |

| Watchdog timer                                          | WDTIFG                                                                                 | Maskable                                             | 0FFF4h       | 10          |

| Timer_A                                                 | CCIFG0 (see Note 2)                                                                    | Maskable                                             | 0FFF2h       | 9           |

| Timer_A                                                 | CCIFG1, CCIFG2, TAIFG (see Notes 1 and 2)                                              | Maskable                                             | 0FFF0h       | 8           |

| USART0 receive (see Note 5)                             | URXIFG.0                                                                               | Maskable                                             | 0FFEEh       | 7           |

| USART0 transmit (see Note 5)                            | UTXIFG.0                                                                               | Maskable                                             | 0FFECh       | 6           |

| ADC10                                                   | ADC10IFG                                                                               | Maskable                                             | 0FFEAh       | 5           |

|                                                         |                                                                                        |                                                      | 0FFE8h       | 4           |

| I/O Port P2 (eight flags – see Note 3)                  | P2IFG.0 to P2IFG.7<br>(see Notes 1 and 2)                                              | Maskable                                             | 0FFE6h       | 3           |

| I/O Port P1 (eight flags)                               | P1IFG.0 to P1IFG.7<br>(see Notes 1 and 2)                                              | Maskable                                             | 0FFE4h       | 2           |

|                                                         |                                                                                        |                                                      | 0FFE2h       | 1           |

|                                                         |                                                                                        |                                                      | 0FFE0h       | 0, lowest   |

NOTES: 1. Multiple source flags

2. Interrupt flags are located in the module

3. There are eight Port P2 interrupt flags, but only six Port P2 I/O pins (P2.0–5) are implemented on the 11x2 and 12x2 devices.

4. (Non)-maskable: the individual interrupt enable bit can disable an interrupt event, but the general interrupt enable cannot.

5. USART0 is implemented in MSP430x12x2 only.

SLAS361 - DECEMBER 2001

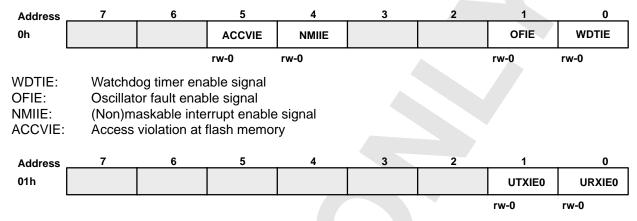

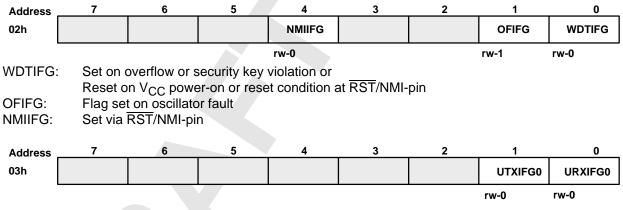

## special function registers

Most interrupt and module enable bits are collected into the lowest address space. Special function register bits that are not allocated to a functional purpose are not physically present in the device. Simple software access is provided with this arrangement.

#### interrupt enable 1 and 2

URXIE0: USART0, UART, and SPI receive-interrupt-enable signal (not present on MSP430x11x2 devices) UTXIE0: USART0, UART, and SPI transmit-interrupt-enable signal (not present on MSP430x11x2 devices)

#### interrupt flag register 1 and 2

URXIFG0: USART0, UART, and SPI receive flag (not present on MSP430x11x2 devices) UTXIFG0: USART0, UART, and SPI transmit flag (not present on MSP430x11x2 devices)

SLAS361 - DECEMBER 2001

#### boot ROM containing bootstrap loader

The bootstrap loader downloads data into the flash memory module. Various write, read, and erase operations are needed for a proper download environment. The bootstrap loader is only available on F devices.

#### functions of the bootstrap loader:

Definition of read: write: apply and transmit data of peripheral registers or memory to pin P1.1 (BSLTX) read data from pin P2.2 (BSLRX) and write them into flash memory

#### unprotected functions

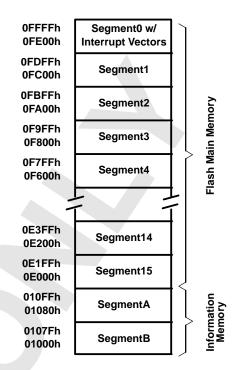

Mass erase, erase of the main memory (Segment0 to Segment7/15) Access to the MSP430 via the bootstrap loader is protected. It must be enabled before any protected function can be performed. The 256 bits in 0FFE0h to 0FFFFh provide the access key.

#### protected functions

All protected functions can be executed only if the access is enabled.

- Write/program byte into flash memory; Parameters passed are start address and number of bytes (the block-write feature of the flash memory is not supported and not useful with the UART protocol).

- Segment erase of Segment0 to Segment7/15 in the main memory and segment erase of SegmentA and SegmentB in the information memory.

- Read all data in main memory and information memory.

- Read and write to all byte peripheral modules and RAM.

- Modify PC and start program execution immediately.

#### NOTE:

Unauthorized readout of code and data is prevented by the user's definition of the data in the interrupt memory locations. Also, blowing the security fuse prevents read out of the flash data via JTAG.

#### features of the bootstrap loader are:

- UART communication protocol, fixed to 9600 baud

- Port pin P1.1 for transmit, P2.2 for receive

- TI standard serial protocol definition

- Implemented in flash memory version only

- Program execution starts with the user vector at 0FFFEh or with the bootstrap loader (start vector is at address 0C00h)

#### hardware resources used for serial input/output:

- Pins P1.1 and P2.2 for serial data transmission

- Test and RST/NMI to start program execution at the reset or bootstrap loader vector

- Basic clock module: Rsel=5, DCO=4, MOD=0, DCOCLK for MCLK and SMCLK, clock divider for MCLK and SMCLK at default: dividing by 1

- Timer\_A: Timer\_A operates in continuous mode with MCLK source selected, input divider set to 1, using CCR0, and polling of CCIFG0.

- WDT: Watchdog timer is halted

- Interrupt: GIE=0, NMIIE=0, OFIE=0, ACCVIE=0

- Memory allocation and stack pointer:

- If the stack pointer points to RAM addresses above 0220h, 6 bytes of the stack are allocated plus RAM addresses 0200h to 0219h. Otherwise the stack pointer is set to 0220h and allocates RAM from 0200h to 021Fh.

SLAS361 - DECEMBER 2001

## boot ROM containing bootstrap loader (continued)

NOTE: bootstrap loader take care th:

When writing RAM data via bootstrap loader, take care that the stack is outside the range of the data being written.

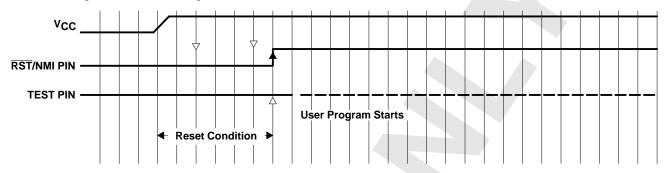

Program execution begins with the user's reset vector at FFFEh (standard method) if TEST is held low while RST/NMI goes from low to high:

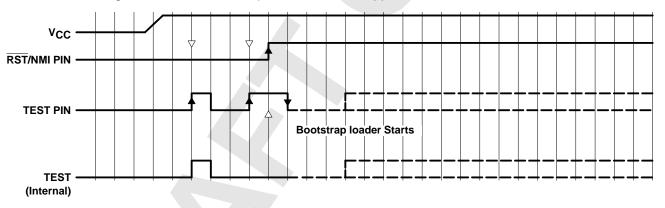

Program execution begins with the bootstrap vector at 0C00h (boot ROM) if a minimum of two positive edges have been applied to TEST while RST/NMI is low, and TEST is high when RST/NMI goes from low to high. The TEST signal is normally used internally to switch pins P1.4, P1.5, P1.6, and P1.7 between their application function and the JTAG function. If the second rising edge at TEST is applied while RST/NMI is held low, the internal TEST signal is held low and the pins remain in the application mode:

Test mode can be entered again after TEST is taken low and then back high.

The bootstrap loader will not be started (via the vector in address 0C00h), if:

- There were less than two positive edges at TEST while RST/NMI is low

- TEST is low if RST/NMI goes from low to high

- JTAG has control over the MSP430 resources

- Supply voltage VCC drops and a POR is executed

- RST/NMI is operating as (non)maskable NMI function but NMI bit in watchdog control register remains unchanged. The bootstrap loader may not be disturbed when the RST/NMI pin is pulled low.

SLAS361 - DECEMBER 2001

#### flash memory

The flash memory consists of 512-byte segments in the main memory and 128-byte segments in the information memory. See device memory maps for specific device information.

Segment0 to Segment7/15 can be erased individually, or altogether as a group.

SegmentA and SegmentB can be erased individually, or as a group with segments 0–7/15.

The memory in SegmentA and SegmentB is also called *Information Memory.*

VPP is generated internally. VCC current increases during programming.

During program/erase cycles, VCC must not drop below the minimum specified for program/erase operation.

Program and erase timings are controlled by the flash timing generator—no software intervention is needed. The input frequency of the flash timing generator should be in the proper range and must be applied until the write/program or erase operation is completed.

NOTE: All segments not implemented on all devices.

During program or erase, no code can be executed from flash memory and all interrupts must be disabled by setting the GIE, NMIE, ACCVIE, and OFIE bits to zero. If a user program requires execution concurrent with a flash program or erase operation, the program must be executed from memory other than the flash memory (e.g., boot ROM, RAM). In the event a flash program or erase operation is initiated while the program counter is pointing to the flash memory, the CPU will execute JMP \$ instructions until the flash program or erase operation is completed. Normal execution of the previously running software then resumes.

Unprogrammed, new devices may have some bytes programmed in the information memory (needed for test during manufacturing). The user should perform an erase of the information memory prior to first use.

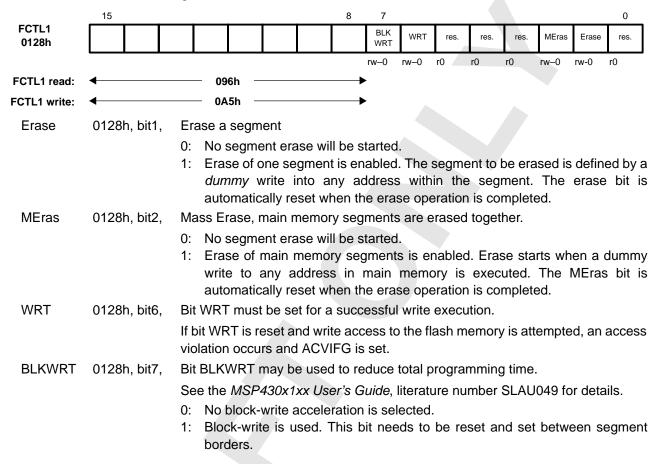

#### flash memory control register FCTL1

All control bits are reset during PUC. PUC is active after  $V_{CC}$  is applied, a reset condition is applied to the RST/NMI pin, the watchdog timer expires, a watchdog access violation occurs, or an improper flash operation has been performed. A more detailed description of the control-bit functions is found in the flash memory module description (see the *MSP430x1xx User's Guide*, literature number SLAU049). Any write to control register FCTL1 during erase, mass erase, or write (programming) will end in an access violation with ACCVIFG=1. Special conditions apply for block-write mode. See the *MSP430x1xx User's Guide*, literature number SLAU049 for details.

SLAS361 - DECEMBER 2001

## flash memory control register FCTL1 (continued)

Read access is possible at any time without restrictions.

The control bits of control register FCTL1 are:

## Table 3. Allowed Combinations of Control Bits Allowed for Flash Memory Access

| FUNCTION PERFORMED                                                                           | BLKWRT | WRT | MEras | Erase | BUSY              | WAIT              | Lock |

|----------------------------------------------------------------------------------------------|--------|-----|-------|-------|-------------------|-------------------|------|

| Write word or byte                                                                           | 0      | 1   | 0     | 0     | 0                 | 0                 | 0    |

| Write word or byte in same block, block-write mode                                           | 1      | 1   | 0     | 0     | $0 \rightarrow 1$ | $0 \rightarrow 1$ | 0    |

| Erase one segment by writing to any address in the target segment                            | 0      | 0   | 0     | 1     | 0                 | 0                 | 0    |

| Erase all segments (0 to 7) but not the information memory (segments A and B)                | 0      | 0   | 1     | 0     | 0                 | 0                 | 0    |

| Erase all segments (0 to 7 and A and B) by writing to any address in the flash memory module | 0      | 0   | 1     | 1     | 0                 | 0                 | 0    |

NOTE: The table shows all valid combinations. Any other combination will result in an access violation.

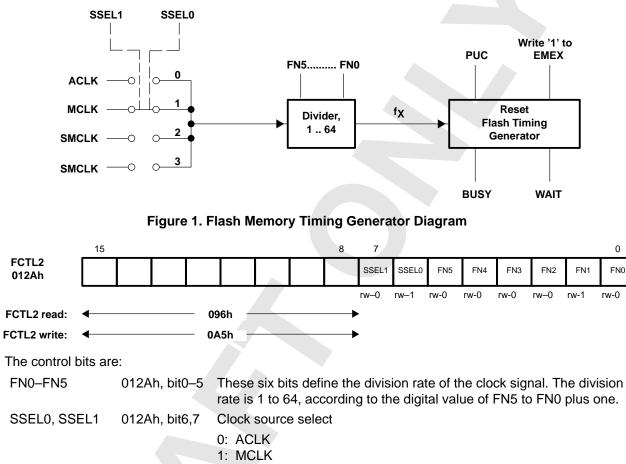

## flash memory, timing generator, control register FCTL2

The timing generator (see Figure 1) generates all the timing signals necessary for write, erase, and mass erase from the selected clock source. One of three different clock sources may be selected by control bits SSEL0 and SSEL1 in control register FCTL2. The selected clock source should be divided to meet the frequency requirements specified in the recommended operating conditions.

SLAS361 - DECEMBER 2001

## flash memory, timing generator, control register FCTL2 (continued)

The flash timing generator is reset with PUC. It is also reset if the emergency exit bit EMEX is set.

Control register FCTL2 may not be written to if the BUSY bit is set; otherwise, an access violation will occur (ACCVIFG=1).

Read access is possible at any time without restrictions.

The flash timing generator is reset with PUC. It is also reset if the EMEX bit is set.

2: SMCLK 3: SMCLK

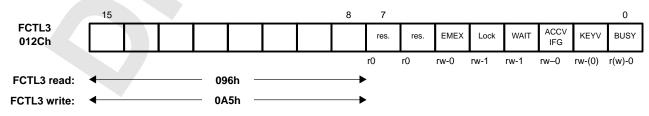

## flash memory control register FCTL3

There are no restrictions to modify this control register.

SLAS361 – DECEMBER 2001

## flash memory control register FCTL3 (continued)

| BUSY     | 012Ch, bit0, | The BUSY bit shows if an access to the flash memory is allowed (BUSY=0), or if an access violation occurs. The BUSY bit is read-only, but a write operation is allowed. The BUSY bit should be tested before each write and erase cycle. The flash timing-generator hardware immediately sets the BUSY bit after start of a write, block-write, erase, or <i>mass</i> erase operation. If the timing generator has completed the operation, the BUSY bit is reset by the hardware. |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |              | No program code can be executed from the <i>busy</i> flash memory during the entire program or erase cycle.                                                                                                                                                                                                                                                                                                                                                                        |

|          |              | 0: Flash memory is not busy.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |              | 1: Flash memory is busy, and remains in busy state if block-write function is in <i>wait</i> mode.                                                                                                                                                                                                                                                                                                                                                                                 |

| KEYV,    | 012Ch, bit1  | Key violation                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |              | 0: Key 0A5h (high byte) was not violated.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |              | 1: Key 0A5h (high byte) was violated. Violation occurs when a write access to registers FCTL1, FCTL2, or FCTL3 is executed and the <i>high byte</i> is not equal to 0A5h. If the security key is violated, bit KEYV is set and a PUC is performed.                                                                                                                                                                                                                                 |

| ACCVIFG, | 012Ch, bit2  | Access violation interrupt flag                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |              | The access-violation flag is set when any combination of control bits other than<br>those shown in Table 3 is attempted, or an instruction is fetched while a<br>block-write operation is active.                                                                                                                                                                                                                                                                                  |

|          |              | Reading the control registers will not set the ACCVIFG bit.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |              | NOTE: The respective interrupt-enable bit ACCVIE is located in the interrupt<br>enable register IE1 in the special function register. The software can set<br>the ACCVIFG bit. If set by software, an NMI is also executed.                                                                                                                                                                                                                                                        |

| WAIT,    | 012CH, bit3  | In the block-write mode, the WAIT bit indicates that data has been written and the flash memory is prepared to receive the next data for programming. The WAIT bit is read only, but a write to the WAIT bit is allowed.                                                                                                                                                                                                                                                           |

|          |              | 0: The block-write operation has began and programming is in progress.                                                                                                                                                                                                                                                                                                                                                                                                             |

|          |              | 1: The block-write operation is active and data programming is complete.                                                                                                                                                                                                                                                                                                                                                                                                           |

## flash memory control register FCTL3 (continued)

| LOCK  | 012Ch, bit4, | The lock bit may be set during any write, segment-erase, or <i>mass</i> -erase requered Any active sequence in progress is completed normally. In segment-write moder the BLKWRT bit is reset and the WAIT bit is set after the mode ends. The lock bit is controlled by software or hardware. If an access violation occurs and the ACCVIFG is set, the LOCK bit is set automatically. |  |  |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       |              | 0: Flash memory may be read, programmed, erased, or mass erased.                                                                                                                                                                                                                                                                                                                        |  |  |

|       |              | 1: Flash memory may be read but not programmed, erased, or <i>mass</i> erased.<br>A current program, erase, or <i>mass</i> -erase operation will complete normally.<br>The access-violation interrupt flag ACCVIFG is set when data are written to<br>the flash memory module while the lock bit is set.                                                                                |  |  |

| EMEX, | 012Ch, bit5, | Emergency exit. The emergency exit should only be used if the flash memory write or erase operation is out of control.                                                                                                                                                                                                                                                                  |  |  |

|       |              | 0: No function.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|       |              | 1: Stops the active operation immediately, and shuts down all internal parts in<br>the flash memory controller. Current consumption immediately drops back<br>to the active mode. All bits in control register FCTL1 are reset. Since the<br>EMEX bit is automatically reset by hardware, the software always reads                                                                     |  |  |

## flash memory, interrupt and security key violation

EMEX as 0.

One NMI vector is used for three NMI events: RST/NMI (NMIIFG), oscillator fault (OFIFG), and flash-memory access violation (ACCVIFG). The software can determine the source of the interrupt request since all flags remain set until they are reset by software. The enable flag(s) should be set simultaneously with one instruction before the return-from-interrupt RETI instruction. This ensures that the stack remains under control. A pending NMI interrupt request does not increase stack demand unnecessarily.

SLAS361 - DECEMBER 2001

**PRODUCT PREVIEW**

SLAS361 - DECEMBER 2001

#### peripherals

Peripherals are connected to the CPU through data, address, and control buses and can be handled easily with memory manipulation instructions.

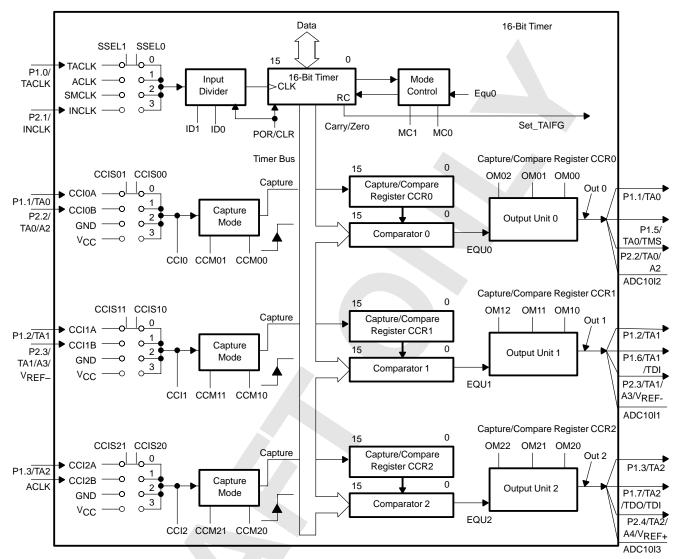

#### oscillator and system clock

Three clocks are used in the system—the system (master) clock MCLK, the subsystem (master) clock SMCLK, and the auxiliary clock ACLK:

Main system clock MCLK, used by the CPU and the system Subsystem clock SMCLK, used by the peripheral modules Auxiliary clock ACLK, originated by LFXT1CLK (crystal frequency) and used by the peripheral modules

After a POR, the DCOCLK is used by default, the DCOR bit is reset, and the DCO is set to the nominal initial frequency. Additionally, if LFXT1CLK (in XT1 mode) fails as the source for MCLK, the DCOCLK is automatically selected to ensure fail-safe operation.

SMCLK can be generated from LFXT1CLK or DCOCLK. ACLK is always generated from LFXT1CLK.

The crystal oscillator can be defined to operate with watch crystals (32768 Hz) or with higher-frequency ceramic resonators or crystals. The crystal or ceramic resonator is connected across two terminals. No external components are required for watch-crystal operation. If the high frequency XT1 mode is selected, external capacitors from XIN to VSS and XOUT to VSS are required as specified by the crystal manufacturer.

The LFXT1 oscillator starts after applying VCC. If the OscOff bit is set to 1, the oscillator stops when it is not used for MCLK. The clock signals ACLK and SMCLK may be used externally via port pins.

Different application requirements and system conditions dictate different system clock requirements, including:

High frequency for quick reaction to system hardware requests or events Low frequency to minimize current consumption, EMI, etc. Stable peripheral clock for timer applications, such as real-time clock (RTC) Start-stop operation to be enabled with minimum delay

SLAS361 – DECEMBER 2001

## oscillator and system clock (continued)

## Figure 3. Clock Signals

Two clock sources, LFXT1CLK and DCOCLK, can be used to drive the MSP430 system. The LFXT1CLK is generated from the LFXT1 crystal oscillator. The LFXT1 crystal oscillator can operate in three modes—low frequency (LF), moderate frequency (XT1), and external input mode. The LFXT1 crystal oscillator may be switched off when it is not in use.

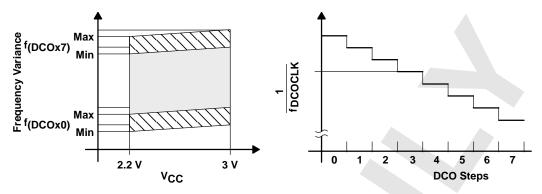

DCOCLK is generated from the DCO. The nominal DCO frequency is defined by the dc generator and can be set by one external resistor, or can be set to one of eight values with integrated resistors. Additional adjustments and modulations of DCOCLK are possible by software manipulation of registers in the DCO module. DCOCLK is stopped automatically when it is not used by the CPU or peripheral modules. The dc generator can be shut down with the SCG0 bit to realize additional power savings when DCOCLK is not in use.

#### NOTE:

The system clock generator always starts with the DCOCLK selected for MCLK (CPU clock) to ensure proper start of program execution. The software defines the final system clock generation through control bit manipulation.

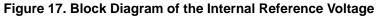

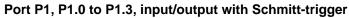

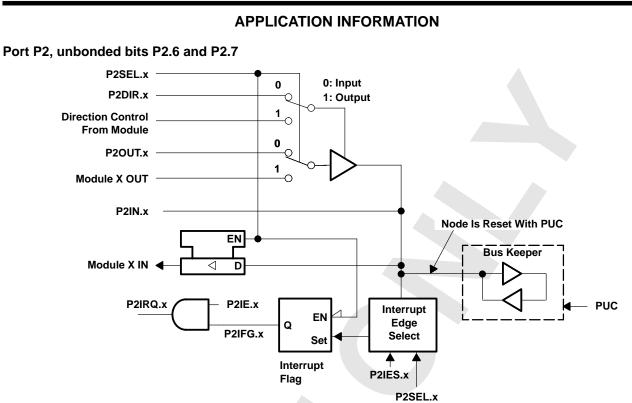

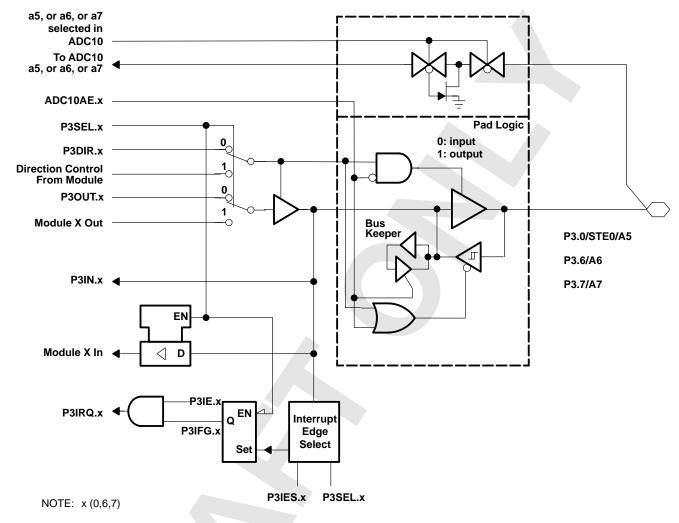

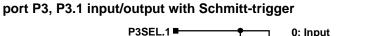

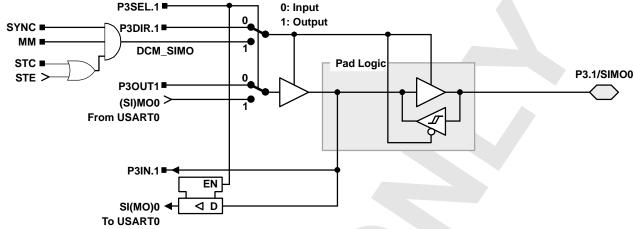

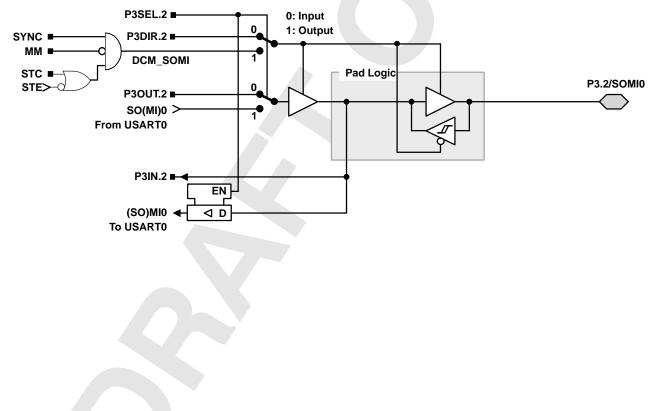

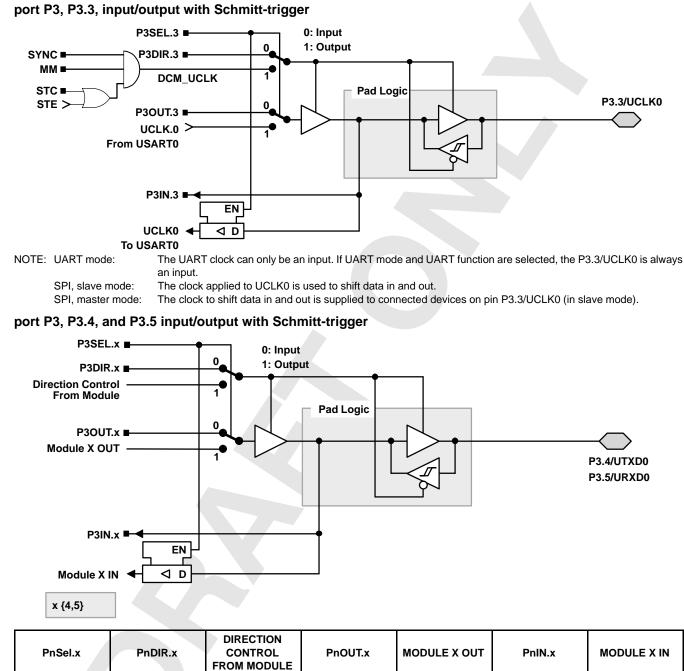

## digital I/O

There are three eight-bit I/O ports, port P1, P2, and P3, implemented (11x2 devices only have six port P2 I/O signals available on external pins and have no port P3). Ports P1 and P2 have seven control registers and port P3 has four control registers to give maximum flexibility of digital input/output to the application:

- All individual I/O bits are programmable independently.

- Any combination of input, output, and interrupt conditions is possible.

- Interrupt processing of external events is fully implemented for all eight bits of port P1 and for six bits of port P2.

- Read/write access to all registers with all instructions

SLAS361 - DECEMBER 2001

## digital I/O (continued)

The seven registers are:

- Input register 8 bits at port P1, P2, P3 Contains information at the pins

- Output register 8 bits at port P1, P2, P3 Contains output information

- Direction register 8 bits at port P1, P2, P3 Controls direction

- Interrupt edge select 8 bits at port P1/P2 Input signal change necessary for interrupt

- Interrupt flags 8 bits at port P1/P2 Indicates if interrupt(s) are pending

- Interrupt enable

8 bits at port P1/P2

Contains interrupt enable bits

- Selection (Port or Mod.) 8 bits at ports P1, P2, P3 Determines if pin(s) have port or module function

All these registers contain eight bits. Two interrupt vectors are implemented: one commonly used for any interrupt event on ports P1.0 to P1.7, and one commonly used for any interrupt event on ports P2.0 to P2.7.

#### NOTE:

Six bits of port P2, P2.0 to P2.5, are available on external pins, but all control and data bits for port P2 are implemented. Port P3 has no interrupt capability. Port P3 is implemented in MSP430x12x2 only.

#### watchdog timer

The primary function of the watchdog timer (WDT) module is to perform a controlled system restart after a software problem has occurred. If the selected time interval expires, a system reset is generated. If this watchdog function is not needed in an application, the module can work as an interval timer, which generates an interrupt after the selected time interval.

The watchdog timer counter (WDTCNT) is a 16-bit up-counter which is not directly accessible by software. The WDTCNT is controlled through the watchdog timer control register (WDTCTL), which is a 16-bit read/write register. Writing to WDTCTL is, in both operating modes (watchdog or timer), only possible by using the correct password in the high-byte. The low-byte stores data written to the WDTCTL. The high-byte must be the password 05Ah. If any value other than 05Ah is written to the high-byte of the WDTCTL, a system reset PUC is generated. When the password is read, its value is 069h. This minimizes accidental write operations to the WDTCTL register. In addition to the watchdog timer control bits, there are two bits included in the WDTCTL register that configure the NMI pin.

## Timer\_A (Three capture/compare registers)

The Timer\_A module offers one sixteen-bit counter and three capture/compare registers. The timer clock source can be selected to come from two external sources TACLK (SSEL=0) or INCLK (SSEL=3), or from two internal sources, the ACLK (SSEL=1) or SMCLK (SSEL=2). The clock source can be divided by one, two, four, or eight. The timer can be fully controlled (in word mode) since it can be halted, read, and written. It can be stopped, run continuously, counted up or up/down, using one compare block to determine the period. The three capture/compare blocks are configured by the application to run in capture or compare mode.

The capture mode is primarily used to measure external or internal events using any combination of positive, negative, or both edges of the signal. Capture mode can be started and stopped by software. Three different external events TA0, TA1, and TA2 can be selected. At capture/compare register CCR2 the ACLK is the capture signal if CCI2B is selected. Software capture is chosen if CCISx=2 or CCISx=3 (see Figure 4).

The compare mode is primarily used to generate timings for the software or application hardware, or to generate pulse-width modulated output signals for various purposes like D/A conversion functions or motor control. An individual output module is assigned to each of the three capture/compare registers. The output modules can run independently of the compare function, or can be triggered in several ways.

SLAS361 - DECEMBER 2001

## Timer\_A (3 capture/compare registers) (continued)

Figure 4. Timer\_A, MSP430x11x2 and MSP430x12x2 Configuration

The Timer\_A module uses two interrupt vectors. One individual vector is assigned to capture/compare block CCR0, and one common interrupt vector is implemented for the timer and the other two capture/compare blocks. The three interrupt events using the same vector are identified by an individual interrupt vector word. The interrupt vector word is used to add an offset to the program counter to continue the interrupt handler software at the corresponding program location. This simplifies the interrupt handler and gives each interrupt event the same overhead of five cycles in the interrupt handler.

## UART With Timer\_A3

Serial communication is implemented by using software and one capture/compare block. The hardware supports the output of the serial-data stream, bit by bit, with the timing determined by the comparator/timer. The data input uses the capture feature. The capture flag finds the start of a character, while the compare feature latches the input-data stream, bit by bit. The software/hardware interface connects the mixed-signal controller to external devices, systems, or networks.

SLAS361 - DECEMBER 2001

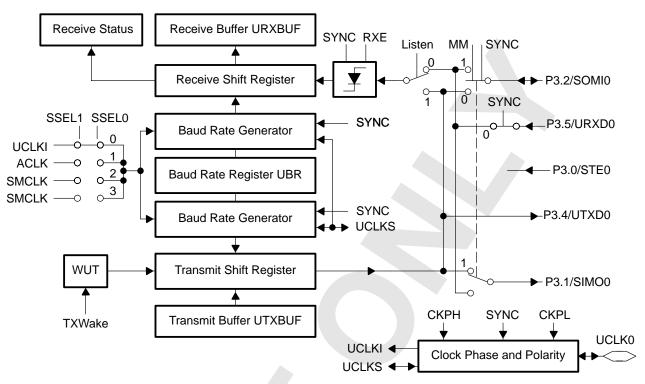

## USART0 (MSP430x12x2 only)

The universal synchronous/asynchronous interface is a dedicated peripheral module used in serial communications.

The USART supports synchronous SPI (3- or 4-pin), and asynchronous UART communication protocols, using double-buffered transmit and receive channels. Data streams of 7 or 8 bits in length can be transferred at a rate determined by the program or by an external clock. Low-power applications are optimized by UART mode options which allow for the reception of only the first byte of a complete frame. The application software should then decide if the succeeding data is to be processed. This option reduces power consumption. Two dedicated interrupt vectors are assigned to the USART0 module—one for the receive and one for the transmit channels.

The USART function is available at the respective pins if bits P3SEL.0 to P3SEL.5 are defined correctly. The P3SEL.x bits determine whether the port function (initial state) or the USART function is connected to the pins.

UART mode on pins P3.4/UTXD0, P3.5/URXD0:

Select bits P3SEL.4 and P3SEL.5 must be set for receive and transmit function. Bit P3SEL.3 is set only if the clock source for the UART is applied on P3.3/UCLK0.

Bits UTXE0 (transmitter enable) and URXE0 (receive enable) must be set.

SPI mode on pins P3.0/STE0 (only in 4-pin mode), P3.1/SIMO0, P3.2/SOMI0, P3.3/UCLK0:

Select bits P3SEL.1, P3SEL.2, and P3SEL.3 must be set.

Select bit P3SEL.0 is set only if 4-pin SPI mode is used.

Bit USPIE0 (SPI enable) must be set.

Note that the SWRST bit in the USART control register is initially set by PUC to reset the USART function. The transmit interrupt flag UTXIFG0 is set (initial state) if the transmitter can accept data for transmission.

SLAS361 - DECEMBER 2001

## USART0 (MSP430x12x2 only) (continued)

Figure 5. Block Diagram of USART

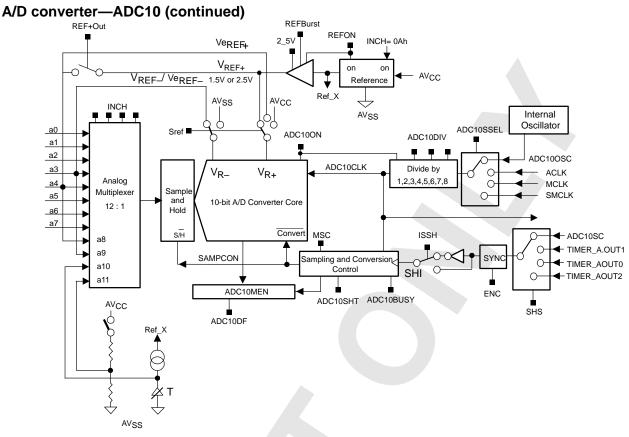

## A/D converter—ADC10

The ADC10 analog-to-digital converter (ADC) uses a 10-bit weighted capacitor array. The CMOS threshold detector in the successive approximation conversion technique determines each bit by examining the charge on a series of binary-weighted capacitors.

The ADC has the following features:

- 10-bit converter with ±1 LSB linearity

- Built-in sample-and-hold with four sample times: 4x, 8x, 16x, or 64xADC10CLK

- Four (MSP430x11x2) or eight (MSP430x12x2) external analog channels and four internal analog channels. The external ADC input terminals are shared with digital port I/O pins.

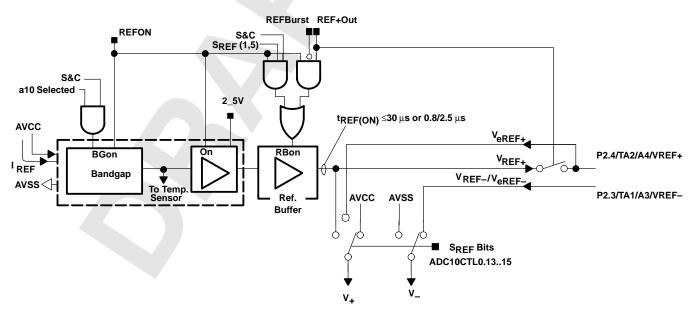

- Internal reference voltage V<sub>(EF+)</sub> of 1.5 V or 2.5 V, software-selectable by control bit 2\_5V

- Internal-temperature sensor for temperature measurement, T = (V\_SENSOR(T) – V\_SENSOR(0°C)) / TC\_SENSOR in °C

- Battery voltage measurement: N =  $0.5 \times (AV_{CC} AV_{SS}) \times 1024/1.5$  V; V REF+ is selected for 1.5 V.

- Source of positive reference voltage level V<sub>R+</sub> can be selected as internal (1.5 V or 2.5 V), external, or AV<sub>CC</sub>.

- Four conversion clock sources: ACLK, MCLK, SMCLK, or the internal ADC10CLK oscillator

- Channel conversion: individual channels, a group of channels, or repeated conversion of a group of channels.

- The conversion can be triggered by software (bit ADC10SC) or by Timer\_A3.

- The conversion result is buffered in ADC10MEM.

SLAS361 - DECEMBER 2001

#### Figure 6. Block Diagram of ADC10

#### operation of the ADC10

The ADC converts the selected analog input to its 10-bit representation and stores the results in the ADC10MEM register. The core uses two programmable/selectable voltage levels ( $V_{R+}$  and  $V_{R-}$ ) to define the upper and lower limits of the conversion range, and to determine the full-scale and zero-scale readings. The digital output is full scale when the input signal is equal to or higher than  $V_{R+}$ , and zero when the input signal is equal to or lower than  $V_{R-}$ . The conversion formula is:

$$N_{ADC} = 1023 \times \frac{\left(V_{IN} - V_{R-}\right)}{\left(V_{R+} - V_{R-}\right)}$$

The reference voltage levels for the ADC can be applied internally ( $AV_{CC}$ ,  $AV_{SS}$ ,  $V_{REF+}$ ) or externally ( $V_{eREF+}$ ,  $V_{REF-}/V_{eREF+}$ ) according to the Sref control bits:

Sref

| 0:    | $V_{R+} = AV_{CC}$                  | and | $V_{R-} = AV_{SS}$                                      |

|-------|-------------------------------------|-----|---------------------------------------------------------|

| 1:    | $V_{R+} = V_{REF+}$                 | and | $V_{R-} = AV_{SS}$                                      |

| 2, 3: | $V_{R+} = V_{eREF+}$                | and | $V_{R-} = AV_{SS}$                                      |

| 4:    | $V_{R+} = AV_{CC}$                  | and | V <sub>R-</sub> =V <sub>REF-</sub> /V <sub>eREF+</sub>  |

| 5:    | $V_{R+} = V_{REF+}$                 | and | V <sub>R-</sub> =V <sub>REF-</sub> /V <sub>eREF+</sub>  |

| 6, 7: | V <sub>R+</sub> =V <sub>eREF+</sub> | and | V <sub>R</sub> -=V <sub>REF</sub> -/V <sub>eREF</sub> + |

|       |                                     |     |                                                         |

(1)

SLAS361 - DECEMBER 2001

## operation of the ADC10 (continued)

The internal reference has to be switched on using bit REFON=1 and should be settled before it is used for conversion.

The CONSEQ control bits can select four operating modes:

- CONSEQ = 0: One single channel is converted once (single-channel-single-conversion mode).

- 1: A sequence of analog inputs, A(INCH) to A0, is converted and then stops (sequence-of-channels mode).

- 2: Repeatedly conversion of one channel. Ends if CONSEQ = 1 or 0 (repeat-singlechannel mode).

- 3: A sequence of conversions is repeated until CONSEQ is set to 0 or 1 (repeatsequence-of-channels).

A conversion is started by setting the start-of-conversion bit ADC10SC, or by Timer\_A3 signals OUT0, OUT1, or OUT2. If CONSEQ = 0, then the next conversion starts automatically after completing the previous conversion (MSC = 1), or it can be started by the next trigger from SW (via ADC10SC), or by Timer\_A3. Conversions can be performed only if the ADCON bit is set. The result is stored in register ADC10MEM and can be read in binary or 2's complement format.

The sample and conversion time is derived from ADC10CLK, which is either the internal ADC10 oscillator, MCLK, ACLK, OR SMCLK. The clocks can be predivided as determined by the three ADC10DIV bits (2<sup>ADC10DIV</sup>).

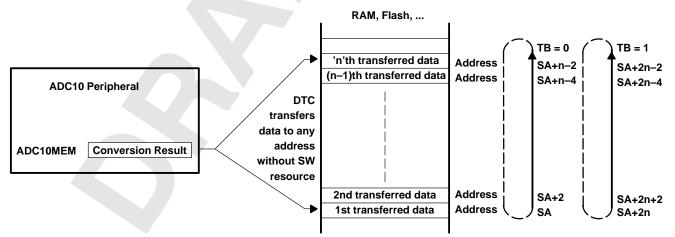

## operation of the ADC10 – data transfer control

The ADC10 includes data transfer control (DTC) logic. The DTC is used to automatically transfer ADC10 conversion results to other memory locations (typically RAM). Often, in microcontroller applications, an end-of-conversion flag or an interrupt flag is polled or an interrupt service request is used to handle the result of A/D conversions. With the DTC hardware of the ADC10, the conversion results can be automatically transferred to a selected destination. No software intervention is required until the predefined number of conversion data has been transferred.

The DTC of ADC10 is especially useful in digital signal processing applications that require high conversion throughput, such as glass breakage sensors, motion detectors, signals prediction (e.g., electronic fuses), high quality voice processing, etc. The DTC concept is shown in the following diagram:

Figure 7. ADC10 Data Transfer Control

SLAS361 - DECEMBER 2001

## peripheral file map

|                       | PERIPHERALS WITH WORD ACCES                   | -                   |               |

|-----------------------|-----------------------------------------------|---------------------|---------------|

| ADC10                 | ADC data transfer start address<br>ADC memory | ADC10SA<br>ADC10MEM | 1BCh<br>1B4h  |

|                       | ADC control register 1                        | ADC10CTL1           | 1B411         |

|                       | ADC control register 0                        | ADC10CTL0           | 1B0h          |

|                       | ADC analog enable                             | ADC10AE             | 04Ah          |

|                       | ADC data transfer control register 1          | ADC10DTC1           | 049h          |

|                       | ADC data transfer control register 1          | ADC10DTC0           | 049h          |

| Timer_A               | Reserved                                      |                     | 017Eh         |

| _                     | Reserved                                      |                     | 017Ch         |

|                       | Reserved                                      |                     | 017Ah         |

|                       | Reserved                                      |                     | 0178h         |

|                       | Capture/compare register                      | CCR2                | 0176h         |

|                       | Capture/compare register                      | CCR1                | 0174h         |

|                       | Capture/compare register                      | CCR0                | 0172h         |

|                       | Timer_A register                              | TAR                 | 0170h         |

|                       | Reserved                                      |                     | 016Eh         |

|                       | Reserved                                      |                     | 016Ch         |

|                       | Reserved                                      |                     | 016Ah         |

|                       | Reserved                                      |                     | 0168h         |

|                       | Capture/compare control                       | CCTL2               | 0166h         |

|                       | Capture/compare control                       | CCTL1               | 0164h         |

|                       | Capture/compare control                       | CCTLO               | 0162h         |

|                       | Timer_A control                               | TACTL               | 0160h         |

|                       | Timer_A interrupt vector                      | TAIV                | 012Eh         |

| Flash Memory          | Flash control 3                               | FCTL3               | 012Ch         |

| -                     | Flash control 2                               | FCTL2               | 012Ah         |

|                       | Flash control 1                               | FCTL1               | 0128h         |

| Watchdog              | Watchdog/timer control                        | WDTCTL              | 0120h         |

|                       | PERIPHERALS WITH BYTE ACCESS                  | 6                   |               |

| USART0                | Transmit buffer                               | UTXBUF.0            | 077h          |

| (in MSP430x12x2 only) | Receive buffer                                | URXBUF.0            | 076h          |

|                       | Baud rate                                     | UBR1.0              | 075h          |

|                       | Baud rate                                     | UBR0.0              | 074h          |

|                       | Modulation control                            | UMCTL.0             | 073h          |

|                       | Receive control                               | URCTL.0             | 072h          |

|                       | Transmit control                              | UTCTL.0             | 071h          |

|                       | UART control                                  | UCTL.0              | 070h          |

| System Clock          | Basic clock sys. control2                     | BCSCTL2             | 058h          |

|                       | Basic clock sys. control1                     | BCSCTL1             | 057h          |

|                       | DCO clock freq. control                       | DCOCTL              | 056h          |

| Port P2               | Port P2 selection                             | P2SEL               | 02Eh          |

|                       | Port P2 interrupt enable                      | P2IE                | 02Dh          |

|                       | Port P2 interrupt edge select                 | P2IES               | 02Ch          |

|                       | Port P2 interrupt flag                        | P2IFG               | 02Bh          |

|                       | Port P2 direction                             | P2DIR               | 02Ah          |

|                       | Port P2 output                                | P2OUT               | 029h          |

|                       | Port P2 input                                 | P2IN                | 028h          |

| Port P1               | Port P1 selection                             | P1SEL               | 026h          |

|                       | Port P1 interrupt enable                      | P1IE                | 025h          |

|                       | Port P1 interrupt edge select                 | P1IES               | 024h          |

|                       | Port P1 interrupt flag                        | P1IFG               | 023h          |

|                       | Port P1 direction                             | P1DIR               | 022h          |

|                       | Port PT direction                             | TIDIK               | 02211         |

|                       | Port P1 output                                | P1OUT               | 02211<br>021h |

SLAS361 - DECEMBER 2001

## peripheral file map (continued)

| PERIPHERALS WITH BYTE ACCESS (CONTINUED) |                                                                                                                                  |                                          |                                              |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------|--|--|

| Port P3<br>(in MSP430x12x2 only)         | Port P3 selection<br>Port P3 direction<br>Port P3 output<br>Port P3 input                                                        | P2SEL<br>P3DIR<br>P3OUT<br>P3IN          | 01Bh<br>01Ah<br>019h<br>018h                 |  |  |

| Special Function                         | Module enable2<br>Module enable1<br>SFR interrupt flag2<br>SFR interrupt flag1<br>SFR interrupt enable2<br>SFR interrupt enable1 | ME2<br>ME1<br>IFG2<br>IFG1<br>IE2<br>IE1 | 005h<br>004h<br>003h<br>002h<br>001h<br>000h |  |  |

## absolute maximum ratings<sup>†</sup>

| Voltage applied at V <sub>CC</sub> to V <sub>SS</sub>       | –0.3 V to 4.1 V                   |

|-------------------------------------------------------------|-----------------------------------|

| Voltage applied to any pin (referenced to V <sub>SS</sub> ) | –0.3 V to V <sub>CC</sub> + 0.3 V |

| Diode current at any device terminal                        | ±2 mA                             |

| Storage temperature, T <sub>stg</sub> (unprogrammed device) | –55°C to 150°C                    |

| Storage temperature, T <sub>stg</sub> (programmed device)   | –40°C to 85°C                     |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE: All voltages referenced to VSS.

## recommended operating conditions

|                                                                       |                                                        |                                                             | MIN     | NOM   | MAX                  | UNITS  |

|-----------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|---------|-------|----------------------|--------|

| Supply voltage during program execution, V                            | CC (see Note 6)                                        | MSP430F11x2                                                 | 1.8     |       | 3.6                  | V      |

| Supply voltage during program/erase flash                             | memory, V <sub>CC</sub>                                | MSP430F12x2                                                 | 2.7     |       | 3.6                  | V      |

| Supply voltage, VSS                                                   |                                                        |                                                             |         | 0     |                      | V      |

| Operating free-air temperature range, $T_A$                           |                                                        | MSP430F11x2<br>MSP430F12x2                                  | -40     |       | 85                   | °C     |

|                                                                       | LF mode selected, XTS=0                                | Watch crystal                                               |         | 32768 |                      | Hz     |

| LFXT1 crystal frequency, f <sub>(LFXT1)</sub><br>(see Note 7)         | VT1 colorited model VTC 1                              | Ceramic resonator                                           | 450     |       | 8000                 | kHz    |

|                                                                       | XT1 selected mode, XTS=1                               | Crystal                                                     | 1000    |       | 8000                 | кни    |

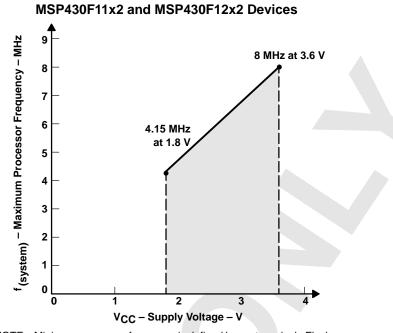

|                                                                       | V <sub>CC</sub> = 1.8 V,<br>MSP430F11x2<br>MSP430F12x2 | dc                                                          |         | 4.15  | MHz                  |        |

| Processor frequency f(system) (MCLK sign                              | ci)                                                    | V <sub>CC</sub> = 3.6 V,<br>MSP430F11x2<br>MSP430F12x2      | dc      |       | 8                    | IVITIZ |

| Flash timing generator frequency, f(FTG)                              |                                                        | MSP430F11x2<br>MSP430F12x2                                  | 257     |       | 476                  | kHz    |

| Cumulative program time, block write, t <sub>(CPT)</sub> (see Note 8) |                                                        | V <sub>CC</sub> = 2.7 V/3.6 V<br>MSP430F11x2<br>MSP430F12x2 |         |       | 3                    | ms     |

| Low-level input voltage (TEST, RST/NMI), VIL (excluding XIN, XOUT)    |                                                        | V <sub>CC</sub> = 2.2 V/3 V                                 | VSS     |       | V <sub>SS</sub> +0.6 | V      |

| High-level input voltage (TEST, RST/NMI), VIH (excluding XIN, XOUT)   |                                                        | V <sub>CC</sub> = 2.2 V/3 V                                 | 0.8VCC  |       | VCC                  | V      |

|                                                                       | VIL(XIN, XOUT)                                         |                                                             | VSS     |       | 0.2×V <sub>CC</sub>  | .,     |

| Input levels at XIN, XOUT                                             | VIH(XIN, XOUT)                                         | $V_{CC} = 2.2 \text{ V/3 V}$                                | 0.8×VCC |       | VCC                  | V      |

NOTES: 6. The LFXT1 oscillator in LF-mode requires a resistor of 5.1 MΩ from XOUT to VSS when VCC <2.5 V.

The LFXT1 oscillator in XT1-mode accepts a ceramic resonator or a crystal frequency of 4 MHz at VCC ≥ 2.2 V.

The LFXT1 oscillator in XT1-mode accepts a ceramic resonator or a crystal frequency of 8 MHz at VCC ≥ 2.8 V.

7. The LFXT1 oscillator in LF-mode requires a watch crystal.

The LFXT1 oscillator in XT1-mode accepts a ceramic resonator or a crystal.

8. The cumulative program time must not be exceeded during a block-write operation.

SLAS361 - DECEMBER 2001

NOTE: Minimum processor frequency is defined by system clock. Flash program or erase operations require a minimum V<sub>CC</sub> of 2.7 V.

#### Figure 8. Frequency vs Supply Voltage

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| supply current (into V <sub>CC</sub> ) excluding extern | nal current (f <sub>(system)</sub> = 1 MHz) |

|---------------------------------------------------------|---------------------------------------------|

|---------------------------------------------------------|---------------------------------------------|

|                                | PARAMETER              | TEST CONDITIONS                                                                    |                             | MIN 1 | ГҮР | MAX | UNIT |

|--------------------------------|------------------------|------------------------------------------------------------------------------------|-----------------------------|-------|-----|-----|------|

|                                |                        | $T_{A} = -40^{\circ}C + 85^{\circ}C,$<br>$f_{MCLK} = f_{(SMCLK)} = 1 \text{ MHz},$ | V <sub>CC</sub> = 2.2 V     |       | 200 | 250 | ۵    |

| I(AM)                          | Active mode            | f(ACLK) = 32,768 Hz,<br>Program executes in Flash                                  | V <sub>CC</sub> = 3 V       |       | 300 | 350 | μA   |

| ( )                            |                        | $T_A = -40^{\circ}C + 85^{\circ}C$ ,                                               | $V_{CC} = 2.2 V$            |       | 3   | 5   |      |

|                                |                        | f(MCLK) = f(SMCLK) = f(ACLK) = 4096 Hz,<br>Program executes in Flash               | V <sub>CC</sub> = 3 V       |       | 11  | 18  | μA   |

| line                           | Low newer mode (LDMO)  | $T_A = -40^{\circ}C + 85^{\circ}C,$                                                | V <sub>CC</sub> = 2.2 V     |       | 32  | 45  | ۸    |

| I(CPUOff) Low-power mode, (LPM | Low-power mode, (LPM0) | f(MCLK) = 0, f(SMCLK) = 1 MHz,<br>f(ACLK) = 32,768 Hz                              | $V_{CC} = 3 V$              |       | 55  | 70  | μA   |

|                                | Low power mode (LDM2)  | $T_A = -40^{\circ}C + 85^{\circ}C,$                                                | $V_{CC}$ = 2.2 V            |       | 11  | 14  |      |

| l(LPM2)                        | Low-power mode, (LPM2) | e, (LPM2)<br>f(MCLK) = f(SMCLK) = 0 MHz,<br>f(ACLK) = 32,768 Hz, SCG0 = 0          | $V_{CC} = 3 V$              |       | 17  | 22  | μA   |

|                                |                        | $T_A = -40^{\circ}C$                                                               |                             |       | 0.8 | 1.2 |      |

|                                |                        | $T_A = 25^{\circ}C$                                                                | V <sub>CC</sub> = 2.2 V     |       | 0.7 | 1   | μA   |